Altera Arria V Hard IP for PCI Express User Manual

Page 141

Chapter 7: IP Core Interfaces

7–43

Avalon-MM Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

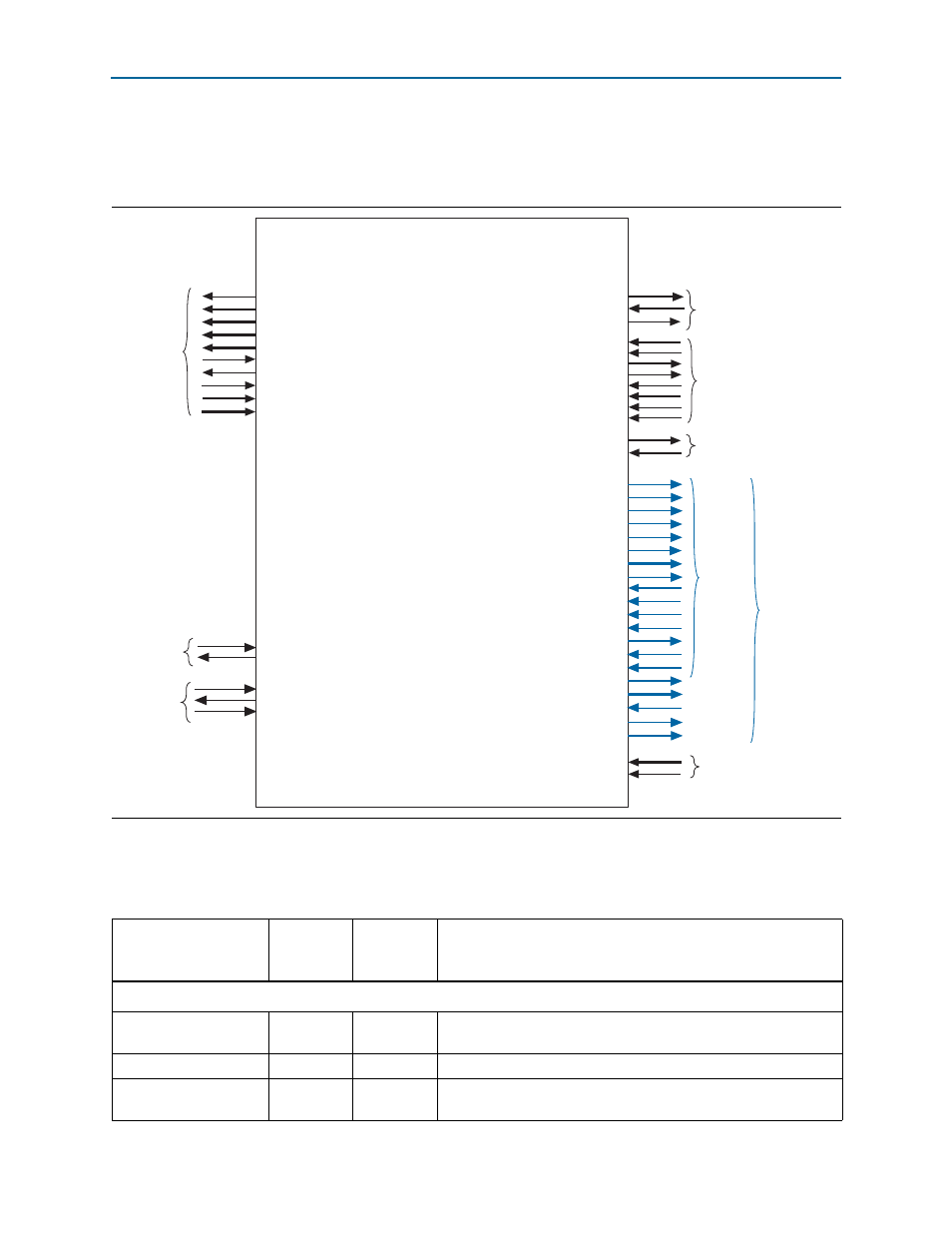

Figure 7–35

illustrates the signals of a completer-only Arria V Hard IP for PCI

Express using the Avalon-MM interface available in the Qsys design flow. This

Endpoint can only accept requests from up-stream devices.

lists the interfaces for these IP cores with links to the sections that describe

them.

Figure 7–35. Signals in the Qsys Avalon-MM Completer-Only Arria V Hard IP for PCI Express

tx_out0[

<n>

:0]

rx_in0[

<n>

:0]

1-Bit Serial

Hard IP for PCI Express IP Core

Completer-Only Single DWord

Test

Interface

test_in[31:0]

simu_mode_pipe

RxmWrite_<n>_o

RxmAddress_<n>_o[31:0]

RxmWriteData_<n>_o[

<w>

-1:0]

RxmByteEnable_<n>_o[<w>-1/8:0]

RxmBurstCount_<n>_o[6 or 5:0]

RxmWaitRequest_<n>_o

RxmRead_<n>_o

RxmReadData_<n>[

<w>

-1:0]_i

RxmReadDataValid_<n>_i

RxmIrq[<m>:0]_i, <m> < 16

64-Bit

Avalon-MM TX

Master Port

reconfig_fromxcvr[<n>69-1:0]

reconfig_toxcvr[<n>45-1:0]

busy_xcvr_reconfig

reconfig_mgmt_address[6:0]

reconfig_mgmt_read

reconfig_mgmt_readdata[31:0]

reconfig_mgmt_waitrequest

reconfig_mgmt_write

reconfig_mgmt_writedata[31:0]

mgmt_rst_reset

mgmt_clk_clk

Transceiver

Reconfiguration

Reconfiguration

Management

Interface

txdatak0

txdata0[7:0]

txdetectrx0

txelectidle0

rxpolarity0

txcompl0

powerdown0[1:0]

tx_deemph0

rxdatak0

rxdata0[7:0]

rxvalid0

phystatus0

eidleinfersel0[2:0]

rxelectidle0

rxstatus0[2:0]

sim_ltssmstate[4:0]

sim_pipe_rate0[1:0]

sim_pipe_pclk_in

txswing0

txmargin0[2:0]

PIPE Interface

Simulation Only

8-Bit PIPE

Clocks

npor

nreset_status

pin_perstn

Reset &

Lock Status

refclk

coreclkout_hip

Table 7–20. Signal Groups in the Avalon-MM Arria V Hard IP for PCI Express Variants (Part 1 of 2)

Signal Group

Full

Featured

Completer

Only Single

DWord

Description

Logical

Avalon-MM CRA Slave

v

—

“32-Bit Non-Bursting Avalon-MM Control Register Access (CRA)

Slave Signals” on page 7–44

Avalon-MM RX Master

v

v

“RX Avalon-MM Master Signals” on page 7–45

Avalon-MM TX Slave

v

—

“64- or 128-Bit Bursting TX Avalon-MM Slave Signals” on

page 7–45