Transaction layer configuration space signals, Transaction layer configuration space signals –30 – Altera Arria V Hard IP for PCI Express User Manual

Page 128

7–30

Chapter 7: IP Core Interfaces

Arria V Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

f

For a description of the completion rules, the completion header format, and

completion status field values, refer to Section 2.2.9 of

.

Transaction Layer Configuration Space Signals

Table 7–11

describes the Transaction Layer Configuration Space signals.

cpl_err[6:0]

(continued)

■

cpl_err[6]

: Log header. If header logging is required, this bit must be set in

every cycle in which any of

cpl_err[2]

,

cpl_err[3]

,

cpl_err[4]

, or

cpl_err[5]

is asserted. The Application Layer presents the header to the

Hard IP by writing the following values to the following 4 registers using LMI

before asserting

cpl_err[6]

:

■

lmi_addr: 12'h81C,

lmi_din

:

err_desc_func0[127:96]

■

lmi_addr: 12'h820,

lmi_din

:

err_desc_func0[95:64]

■

lmi_addr: 12'h824,

lmi_din

:

err_desc_func0[63:32]

■

lmi_addr: 12'h828,

lmi_din

:

err_desc_func0[31:0]

Refer to the

for more information about LMI

signalling.

Due to clock-domain synchronization circuitry,

cpl_err

is limited to at most 1

assertion every 8

pld_clk

cycles. Whenever

cpl_err

is asserted,

cpl_err_func[2:0]

should be updated in the same cycle.

cpl_err_func[2:0]

I

Specifies which function is requesting the

cpl_err

. Must be asserted when

cpl_err

asserts. Due to clock-domain synchronization circuitry,

cpl_err

is

limited to at most 1 assertion every 8

pld_clk

cycles. Whenever

cpl_err

is

asserted,

cpl_err_func[2:0]

should be updated in the same cycle.

cpl_pending[7:0]

I

Completion pending. The Application Layer must assert this signal when a

master block is waiting for completion, for example, when a transaction is

pending. This is a level sensitive input. A bit is provided for each function, where

bit 0 corresponds to function 0, and so on.

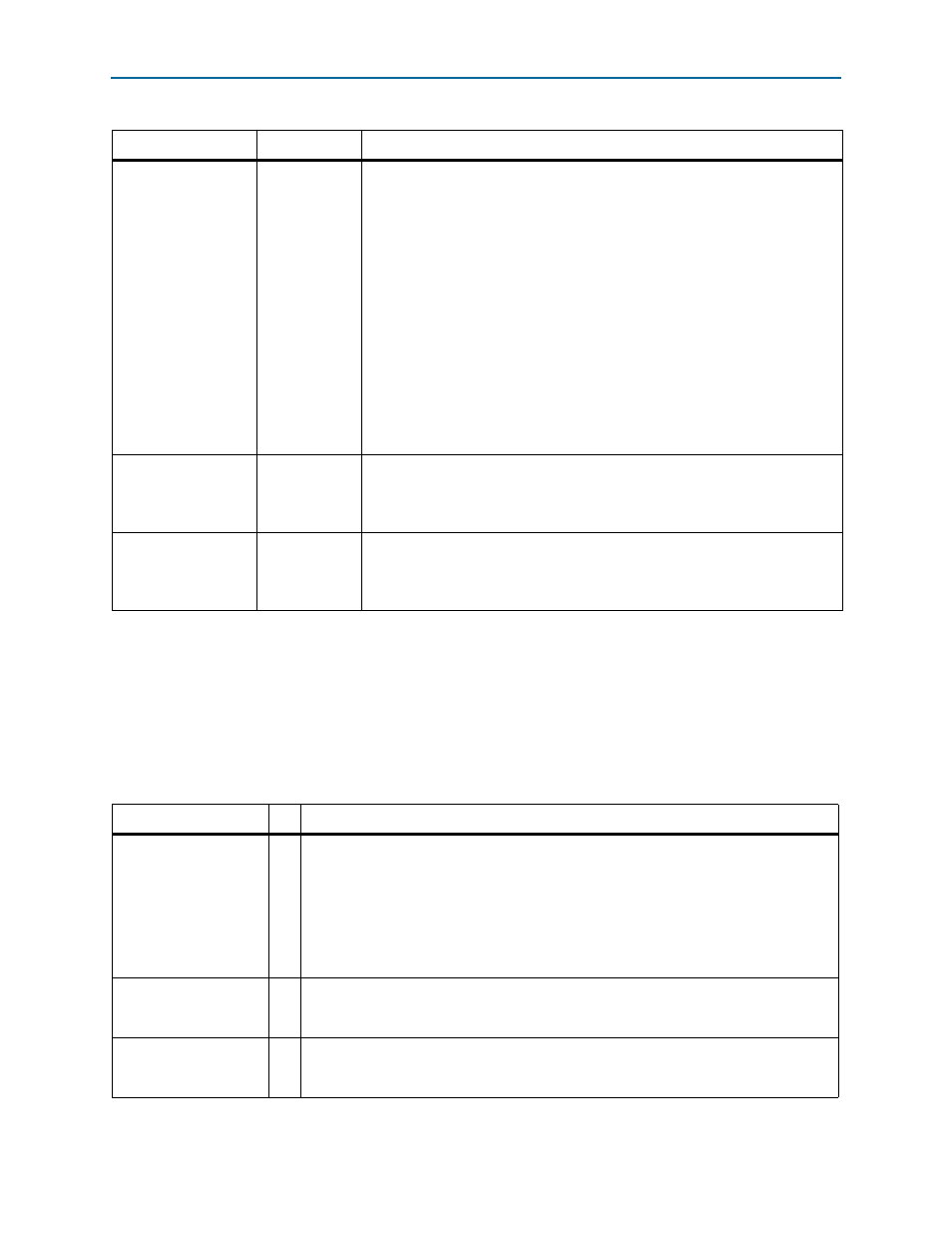

Table 7–10. Completion Signals for the Avalon-ST Interface (Part 2 of 2)

Signal

I/O

Description

Table 7–11. Configuration Space Signals (Hard IP Implementation) (Part 1 of 2)

Signal

Dir

Description

tl_cfg_add[6:0]

0

Address of the register that has been updated. This signal is an index indicating which

Configuration Space register information is being driven onto

tl_cfg_ctl.

The indexing

is defined in

.The index increments every 8

coreclkout_hip

cycles. The index consists of the following 2 pars:

■

[6:4] - indicates the function number whose information is being presented on

tl_cfg_ctl

■

[3:0] - the

tl_cfg_ctl

multiplexor index

tl_cfg_ctl[31:0]

0

The

tl_cfg_ctl

signal is multiplexed and contains the contents of the Configuration

Space registers. The information presented on this bus depends on the

tl_cfg_add

index

according to

tl_cfg_ctl_wr

0

Write signal. This signal toggles when

tl_cfg_ctl

has been updated (every 8

core_clk

cycles). The toggle edge marks where the

tl_cfg_ctl

data changes. You can use this

edge as a reference to determine when the data is safe to sample.