Altera Arria V Hard IP for PCI Express User Manual

Page 71

Chapter 5: Parameter Settings for the Avalon-MM Arria V Hard IP for PCI Express

5–7

PCI Express/PCI Capabilities

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

MSI-X

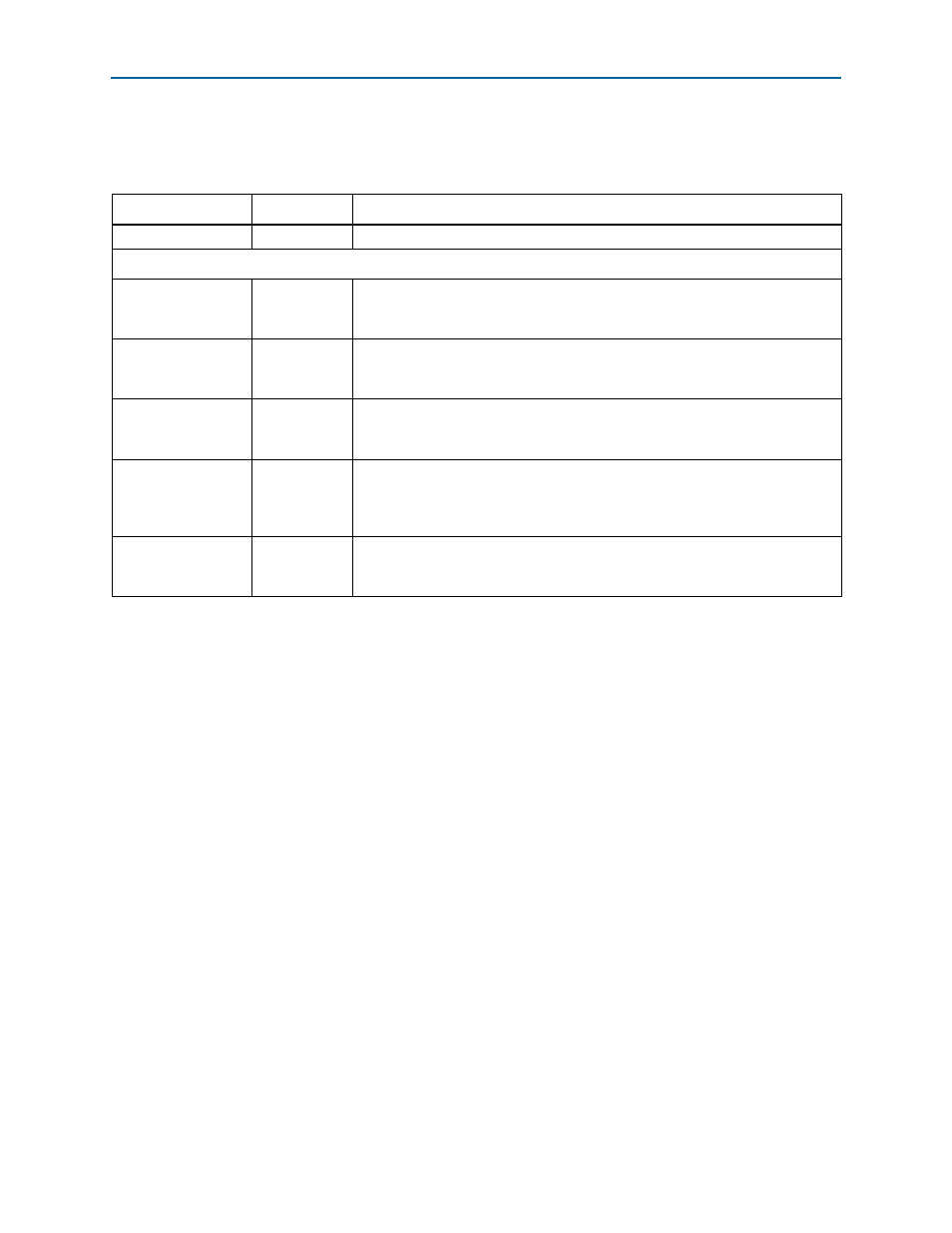

Table 5–7

describes the MSI-X Capabilities register parameters.

Table 5–8. MSI and MSI-X Capabilities

Parameter

Value

Description

Implement MSI-X

On/Off

When On, enables the MSI-X functionality.

Bit Range

Table size

[26:16]

[10:0]

System software reads this field to determine the MSI-X Table size <n>, which is

encoded as <n–1>. For example, a returned value of 2047 indicates a table size of

2048. This field is read-only. Legal range is 0–2047 (2

11

).

Table Offset

[31:0]

Points to the base of the MSI-X Table. The lower 3 bits of the table BAR indicator

(BIR) are set to zero by software to form a 32-bit qword-aligned offset. This field is

read-only. Legal range is 0–2

28

.

Table BAR Indicator

[2:0]

Specifies which one of a function’s BARs, located beginning at 0x10 in

Configuration Space, is used to map the MSI-X table into memory space. This field

is read-only. Legal range is 0–5.

Pending Bit Array

(PBA) Offset

[31:0]

Used as an offset from the address contained in one of the function’s Base

Address registers to point to the base of the MSI-X PBA. The lower 3 bits of the

PBA BIR are set to zero by software to form a 32-bit qword-aligned offset. This

field is read-only. Legal range is 0–2

28

.

PBA BAR Indicator

(BIR)

[2:0]

Indicates which of a function’s Base Address registers, located beginning at 0x10

in Configuration Space, is used to map the function’s MSI-X PBA into memory

space. This field is read-only. Legal range is 0–5.