Interrupts for root ports, Completion side band signals – Altera Arria V Hard IP for PCI Express User Manual

Page 126

7–28

Chapter 7: IP Core Interfaces

Arria V Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Interrupts for Root Ports

Table 7–9

describes the signals available to a Root Port to handle interrupts.

Completion Side Band Signals

describes the signals that comprise the completion side band signals for the

Avalon-ST interface. The Arria V Hard IP for PCI Express provides a completion

error interface that the Application Layer can use to report errors, such as

programming model errors. When the Application Layer detects an error, it can assert

the appropriate

cpl_err

bit to indicate what kind of error to log. The Hard IP sets the

appropriate status bits for the errors in the Configuration Space, and automatically

sends error messages in accordance with the

PCI Express Base Specification

. Note that

the Application Layer is responsible for sending the completion with the appropriate

completion status value for non-posted requests. Refer to

for information on errors that are automatically detected and handled by the Hard IP.

app_msi_func[2:0]

I

Indicates which function is asserting an interrupt with 0 corresponding to function 0, 1

corresponding to function 1, and so on.

app_int_sts_vec[7:0]

I

Level active interrupt signal. Bit 0 corresponds to function 0, and so on. Drives the INTx

line for that function. The core maps this status to INT A/B/C/D according to each

function’s

Interrupt_Pin

register. The core internally wire-ORs the INT requests from

all sources, and generates INT MSGs on the rising/falling edges of the wire-ORed result.

The core logs the

tl_app_int_sts_vec

status in each functions’ PCI Status register.

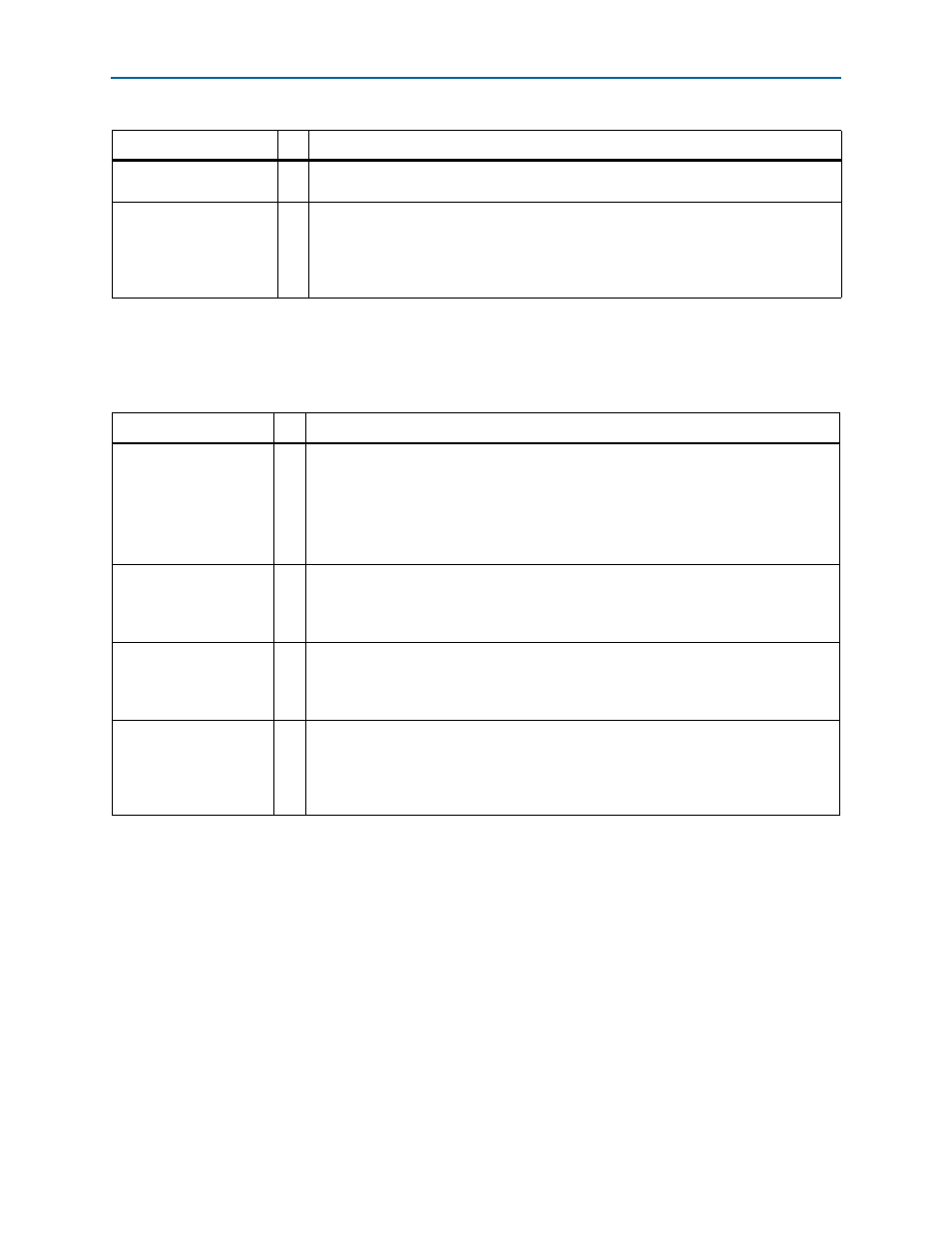

Table 7–8. Interrupt Signals for Endpoints (Part 2 of 2)

Signal

I/O

Description

Table 7–9. Interrupt Signals for Root Ports

Signal

I/O

Description

int_status[3:0]

O

These signals drive legacy interrupts to the Application Layer as follows:

■

int_status[0]: interrupt signal A

■

int_status[1]: interrupt signal B

■

int_status[2]: interrupt signal C

■

int_status[3]: interrupt signal D

aer_msi_num[4:0]

I

Advanced error reporting (AER) MSI number. Provides the low-order message data bits to

be sent in the message data field of the MSI messages associated with the AER capability

structure. Only bits that are enabled by the MSI Message Control register are used. For

Root Ports only.

pex_msi_num[4:0]

I

Power management MSI number. This signal provides the low-order message data bits to

be sent in the message data field of MSI messages associated with the PCI Express

capability structure. Only bits that are enabled by the MSI Message Control register are

used. For Root Ports only.

serr_out

O

System Error: This signal only applies to Root Port designs that report each system error

detected, assuming the proper enabling bits are asserted in the

Root

Control

register

and the

Device

Control

register. If enabled,

serr_out

is asserted for a single clock

cycle when a system error occurs. System errors are described in the

2.0

. in the

Root

Control register

.