Running qsys, Running qsys –2 – Altera Arria V Hard IP for PCI Express User Manual

Page 36

3–2

Chapter 3: Getting Started with the Avalon-MM Arria Hard IP for PCI Express

Running Qsys

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

As

Figure 3–1

illustrates, the design example transfers data between an on-chip

memory buffer located on the Avalon-MM side and a PCI Express memory buffer

located on the root complex side. The data transfer uses the DMA component which is

programmed by the PCI Express software application running on the Root Complex

processor. The example design also includes the Transceiver Reconfiguration

Controller which allows you to dynamically reconfigure transceiver settings. This

component is necessary for high performance transceiver designs.

Running Qsys

Follow these steps to launch Qsys:

1. Choose Programs > Altera > Quartus II><version_number> (Windows Start

menu) to run the Quartus II software. Alternatively, you can also use the

Quartus II Web Edition software.

2. On the Quartus II File menu, click New.

3. Select Qsys System File and click OK. Qsys appears.

4. To establish global settings, click the Project Settings tab.

5. Specify the settings in

f

Refer to

me 1 of the Quartus II Handbook for more

information about how to use Qsys, including information about the Project Settings

tab.

h

For an explanation of each Qsys menu item, refer

in Quartus II Help.

1

This example design requires that you specify the same name for the Qsys system as

for the top-level project file. However, this naming is not required for your own

design. If you want to choose a different name for the system file, you must create a

wrapper HDL file that matches the project top level name and instantiate the

generated system.

6. To add modules from the Component Library tab, under Interface Protocols in

the PCI folder, click the Avalon-MM Arria Hard IP for PCI Express component,

then click +Add.

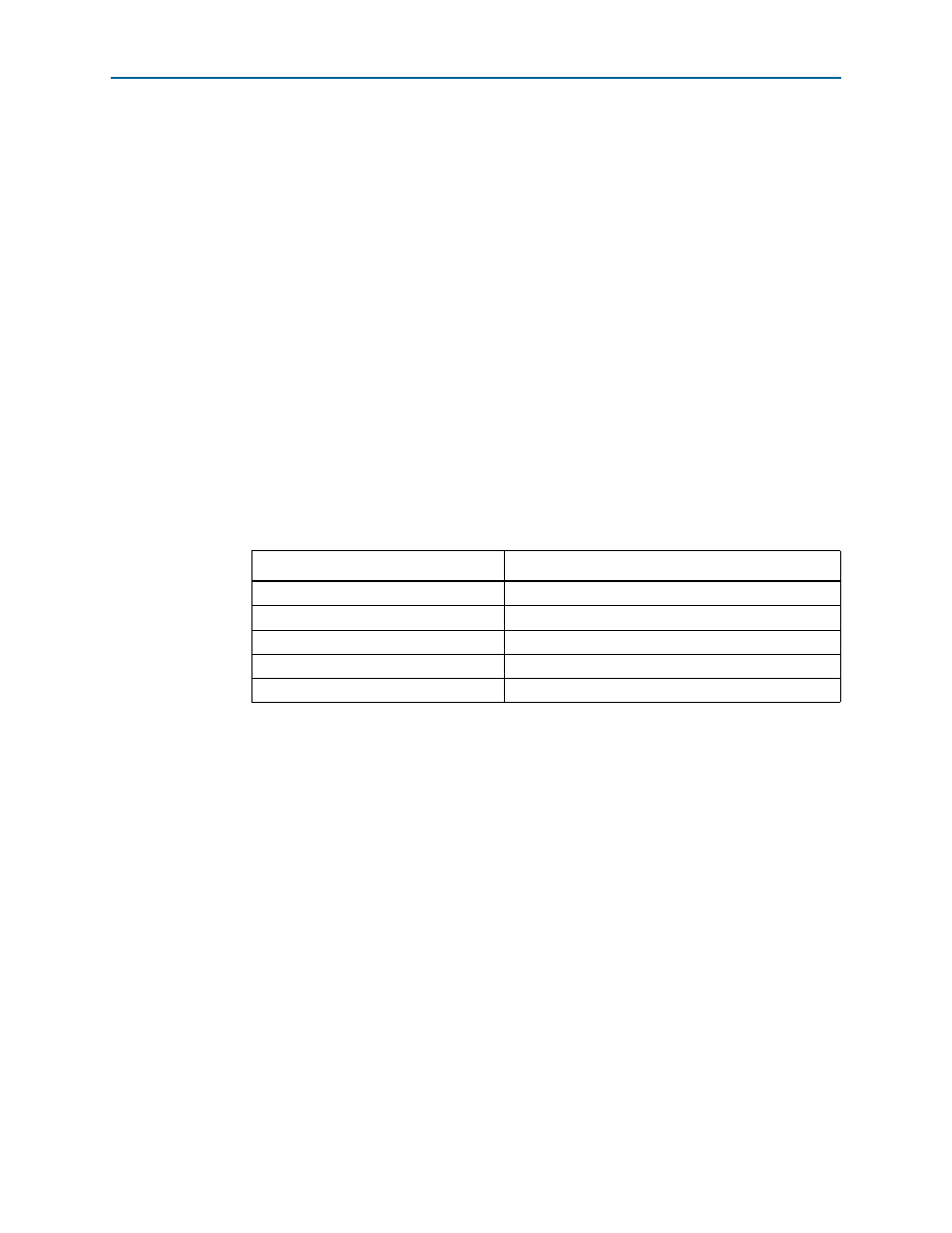

Table 3–1. Project Settings

Parameter

Value

Device family

Device

5AGXFB3H6F40C6ES

Clock crossing adapter type

Handshake

Limit interconnect pipeline stages to

2

Generation Id

0