Qsys design flow, Qsys design flow –9 – Altera Arria V Hard IP for PCI Express User Manual

Page 25

Chapter 2: Getting Started with the Arria Hard IP for PCI Express

2–9

Qsys Design Flow

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Qsys Design Flow

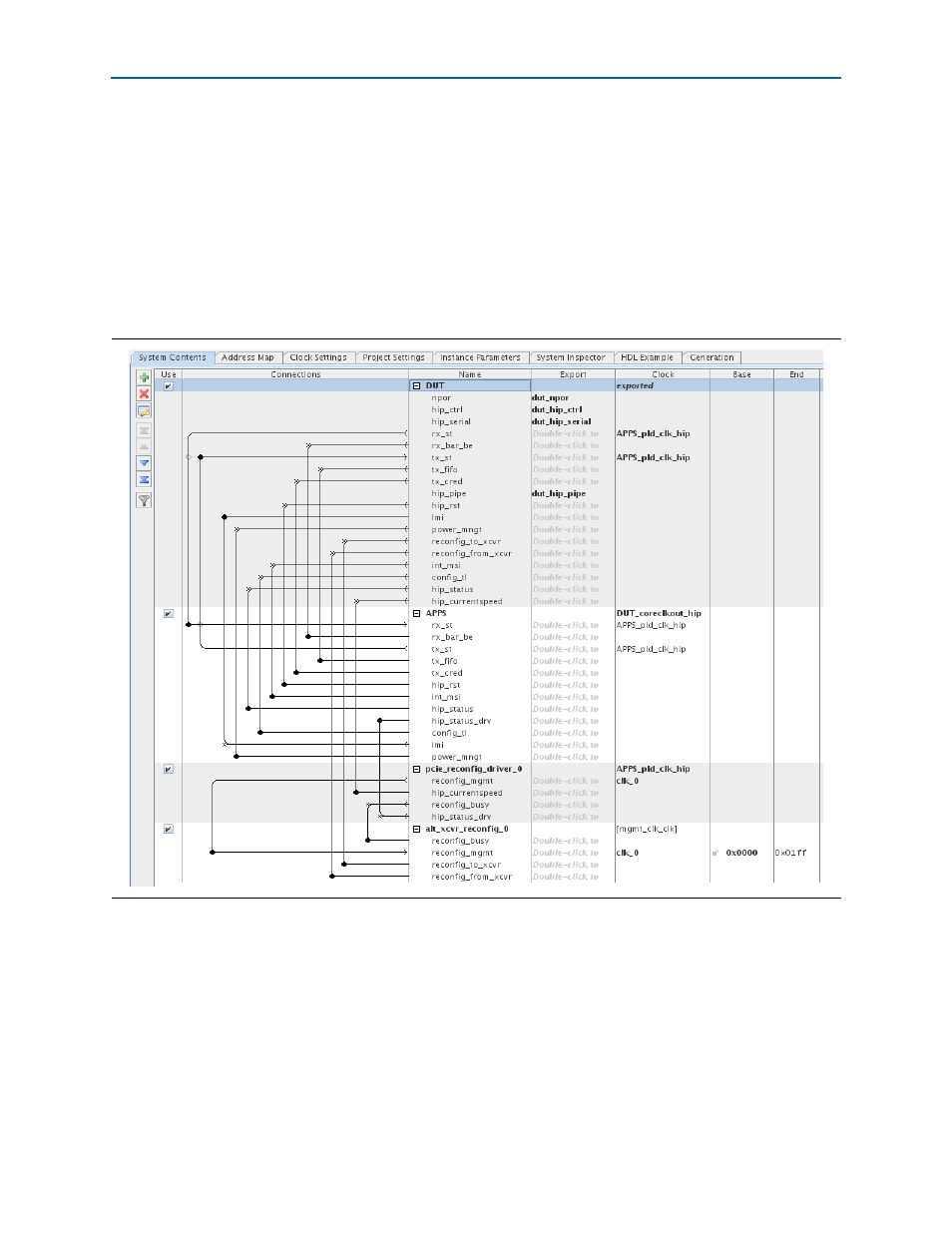

This section guides you through the steps necessary to customize the Arria Hard IP

for PCI Express and run the example testbench in Qsys. Reviewing the Qsys Example

Design for PCIe

For this example, copy the Gen1 x4 Endpoint example design from installation

directory: <install_dir>/ip/altera/altera_pcie/altera_pcie_hip_ast_ed/example_design

/

<device> directory to a working directory.

The following figure illustrates this Qsys system.

The example design includes the following four components:

■

DUT—This is Gen1 x4 Endpoint. For your own design, you can select the data

rate, number of lanes, and either Endpoint or Root Port mode.

■

APPS—This Root Port BFM configures the DUT and drives read and write TLPs to

test DUT functionality. An Endpoint BFM is available if your PCI Express design

implements a Root Port.

Figure 2–5. Complete Gen1 ×4 Endpoint (DUT) Connected to Example Design (APPS)