Ebfm_display verilog hdl function, Ebfm_log_stop_sim verilog hdl function – Altera Arria V Hard IP for PCI Express User Manual

Page 261

Chapter 17: Testbench and Design Example

17–39

BFM Procedures and Functions

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

ebfm_display Verilog HDL Function

The

ebfm_display

procedure or function displays a message of the specified type to

the simulation standard output and also the log file if

ebfm_log_open

is called.

A message can be suppressed, simulation can be stopped or both based on the default

settings of the message type and the value of the bit mask when each of the

procedures listed below is called. You can call one or both of these procedures based

on what messages you want displayed and whether or not you want simulation to

stop for specific messages.

■

When

ebfm_log_set_suppressed_msg_mask

is called, the display of the message

might be suppressed based on the value of the bit mask.

■

When

ebfm_log_set_stop_on_msg_mask

is called, the simulation can be stopped

after the message is displayed, based on the value of the bit mask.

ebfm_log_stop_sim Verilog HDL Function

The

ebfm_log_stop_sim

procedure stops the simulation.

ebfm_log_set_suppressed_msg_mask Verilog HDL Function

The

ebfm_log_set_suppressed_msg_mask

procedure controls which message types

are suppressed.

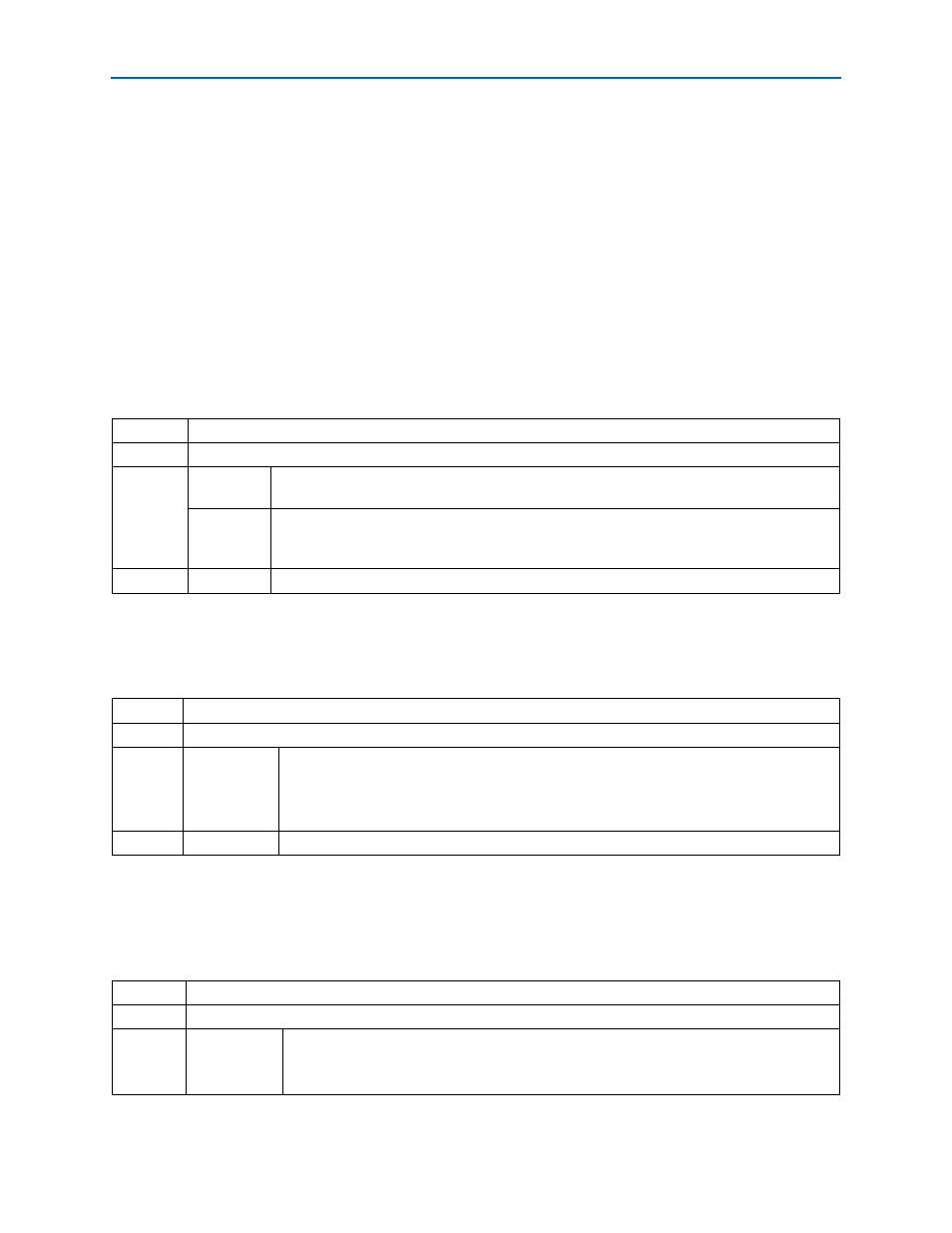

Table 17–37. ebfm_display Procedure

Location

altpcietb_bfm_driver_rp.v

Syntax

Verilog HDL: dummy_return:=ebfm_display(msg_type, message);

Argument

msg_type

Message type for the message. Should be one of the constants defined in

message

The message string is limited to a maximum of 100 characters. Also, because Verilog HDL does

not allow variable length strings, this routine strips off leading characters of 8’h00 before

displaying the message.

Return

always 0

Applies only to the Verilog HDL routine.

Table 17–38. ebfm_log_stop_sim

Location

altpcietb_bfm_driver_rp.v

Syntax

Verilog VHDL:

return:=ebfm_log_stop_sim(success

);

Argument

success

When set to a 1, this process stops the simulation with a message indicating successful

completion. The message is prefixed with

SUCCESS

:.

Otherwise, this process stops the simulation with a message indicating unsuccessful

completion. The message is prefixed with

FAILURE

:.

Return

Always 0

This value applies only to the Verilog HDL function.

Table 17–39. ebfm_log_set_suppressed_msg_mask

Location

altpcietb_bfm_driver_rp.v

Syntax

bfm_log_set_suppressed_msg_mask (msg_mask)

Argument

msg_mask

This argument is

reg [EBFM_MSG_ERROR_CONTINUE: EBFM_MSG_DEBUG].

A 1 in a specific bit position of the

msg_mask

causes messages of the type corresponding to

the bit position to be suppressed.