Altera Arria V Hard IP for PCI Express User Manual

Page 146

7–48

Chapter 7: IP Core Interfaces

Physical Layer Interface Signals

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

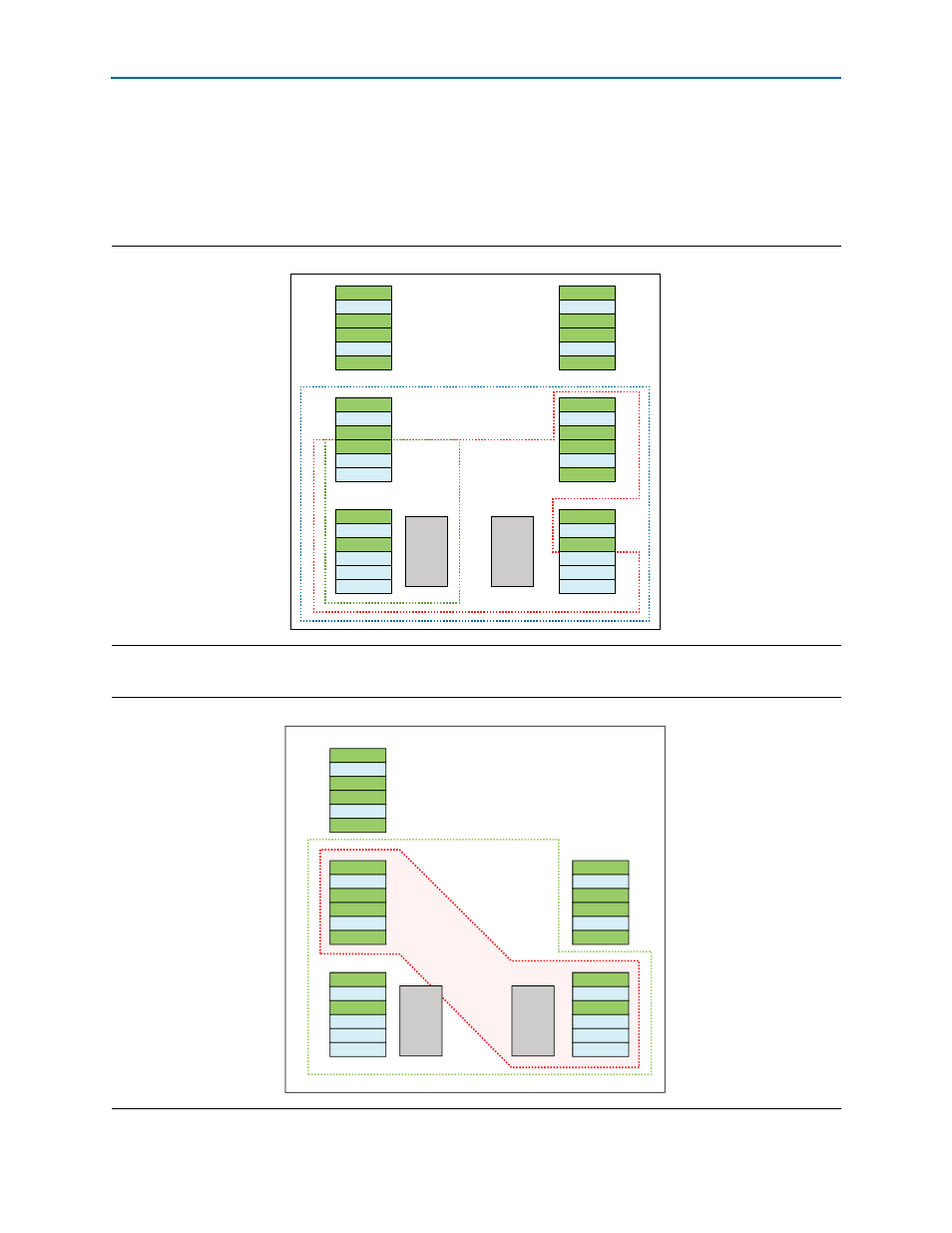

Arria V devices include one or two Hard IP for PCI Express IP Cores. The following

figures illustrates the placement of the Hard IP for PCIe IP cores, transceiver banks

and channels for the largest Arria V devices. Note that the bottom left IP core includes

the CvP functionality. Devices with a single Hard IP for PCIe IP Core only include the

bottom left core.

Figure 7–1. Transceiver Bank and Hard IP for PCI Express IP Core Locations in Arria GX and GT Devices

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

9 Ch

18 Ch

36 Ch

24 Ch

GXB_L2

GXB_L1

GXB_L0

GXB_R2

GXB_R1

GXB_R0

PCIe

Hard IP

with

CvP

PCIe

Hard

IP

Figure 7–2. Transceiver Bank and Hard IP for PCI Express IP Core Locations in Arria SX and ST Devices

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

12 Ch

18 Ch

30 Ch

GXB_L2

GXB_L1

GXB_L0

GXB_R1

GXB_R0

PCIe

Hard IP

with

CvP

PCIe

Hard IP