Avalon-mm-to-pci express address translation table – Altera Arria V Hard IP for PCI Express User Manual

Page 168

8–14

Chapter 8: Register Descriptions

PCI Express Avalon-MM Bridge Control Register Access Content

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

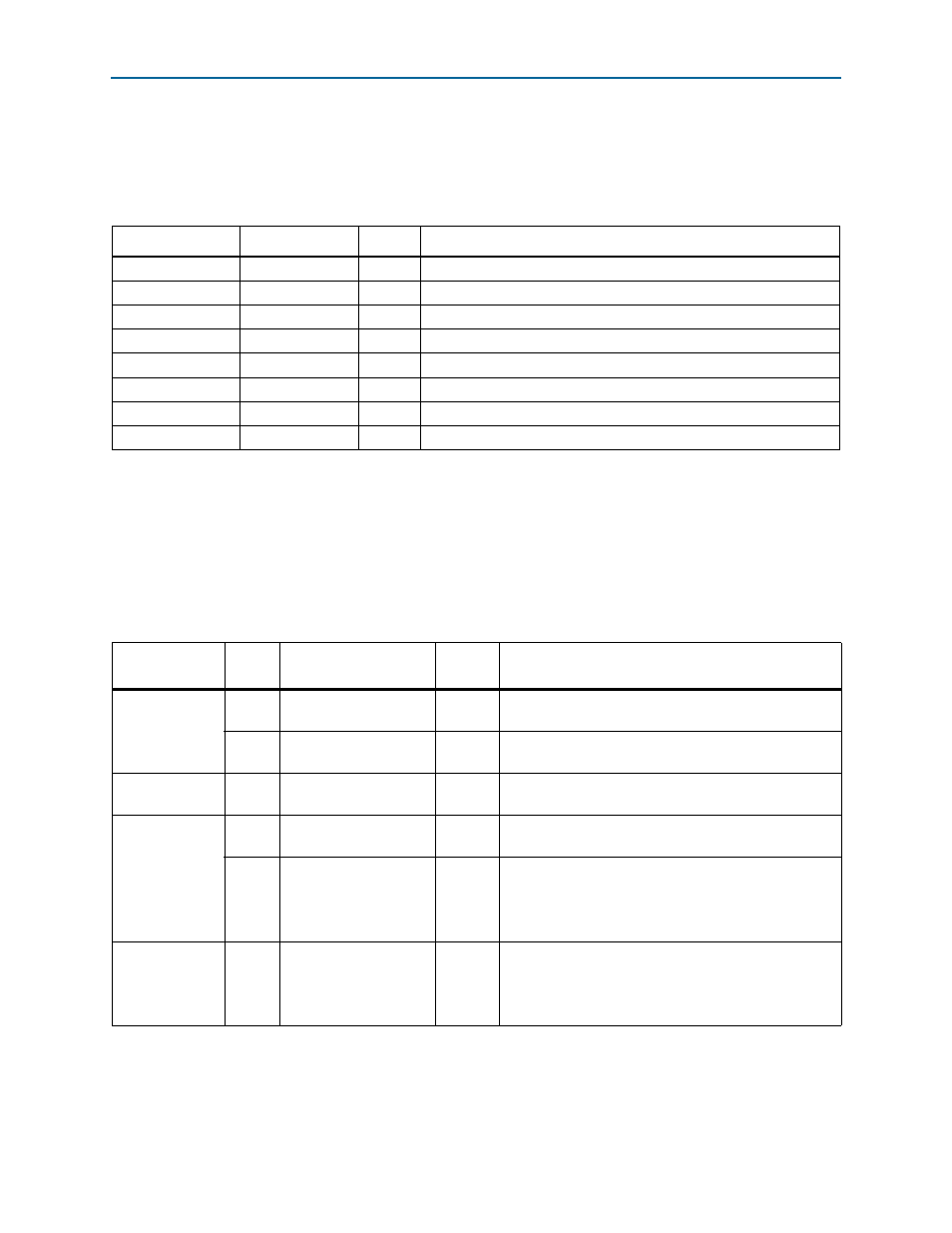

The Avalon-MM-to-PCI Express Mailbox registers are read at the addresses shown in

Table 8–29

. The PCI Express Root Complex should use these addresses to read the

mailbox information after being signaled by the corresponding bits in the PCI Express

Interrupt Status

register.

Avalon-MM-to-PCI Express Address Translation Table

The Avalon-MM-to-PCI Express address translation table is writable using the CRA

slave port. Each entry in the PCI Express address translation table (

Table 8–30

) is 8

bytes wide, regardless of the value in the current PCI Express address width

parameter. Therefore, register addresses are always the same width, regardless of PCI

Express address width.

Table 8–29. Avalon-MM-to-PCI Express Mailbox Registers

0x0900–0x091F

Address

Name

Access

Description

0x0900

A2P_MAILBOX0

RO

Avalon-MM-to-PCI Express Mailbox 0

0x0904

A2P_MAILBOX1

RO

Avalon-MM-to-PCI Express Mailbox 1

0x0908

A2P_MAILBOX2

RO

Avalon-MM-to-PCI Express Mailbox 2

0x090C

A2P_MAILBOX3

RO

Avalon-MM-to-PCI Express Mailbox 3

0x0910

A2P_MAILBOX4

RO

Avalon-MM-to-PCI Express Mailbox 4

0x0914

A2P_MAILBOX5

RO

Avalon-MM-to-PCI Express Mailbox 5

0x0918

A2P_MAILBOX6

RO

Avalon-MM-to-PCI Express Mailbox 6

0x091C

A2P_MAILBOX7

RO

Avalon-MM-to-PCI Express Mailbox 7

Table 8–30. Avalon-MM-to-PCI Express Address Translation Table

0x1000–0x1FFF

Address

Bits

Name

Access

Description

0x1000

[1:0]

A2P_ADDR_SPACE0

RW

Address space indication for entry 0. Refer to

Table 8–31

for the definition of these bits.

[31:2]

A2P_ADDR_MAP_LO0

RW

Lower bits of Avalon-MM-to-PCI Express address map

entry 0.

0x1004

[31:0]

A2P_ADDR_MAP_HI0

RW

Upper bits of Avalon-MM-to-PCI Express address map

entry 0.

0x1008

[1:0]

A2P_ADDR_SPACE1

RW

Address space indication for entry 1. Refer to

Table 8–31

for the definition of these bits.

[31:2]

A2P_ADDR_MAP_LO1

RW

Lower bits of Avalon-MM-to-PCI Express address map

entry 1.

This entry is only implemented if number of address

translation table entries is greater than 1.

0x100C

[31:0]

A2P_ADDR_MAP_HI1

RW

Upper bits of Avalon-MM-to-PCI Express address map

entry 1.

This entry is only implemented if the number of address

translations table entries is greater than 1.

Note to

Table 8–30

:

(1) These table entries are repeated for each address specified in the Number of address pages parameter. If Number of address pages is set to

the maximum of 512, 0x1FF8 contains A2P_ADDR_MAP_LO511 and 0x1FFC contains A2P_ADDR_MAP_HI511.