Ebfm_cfgwr_imm_wait procedure, Ebfm_cfgwr_imm_wait procedure –31 – Altera Arria V Hard IP for PCI Express User Manual

Page 253

Chapter 17: Testbench and Design Example

17–31

BFM Procedures and Functions

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

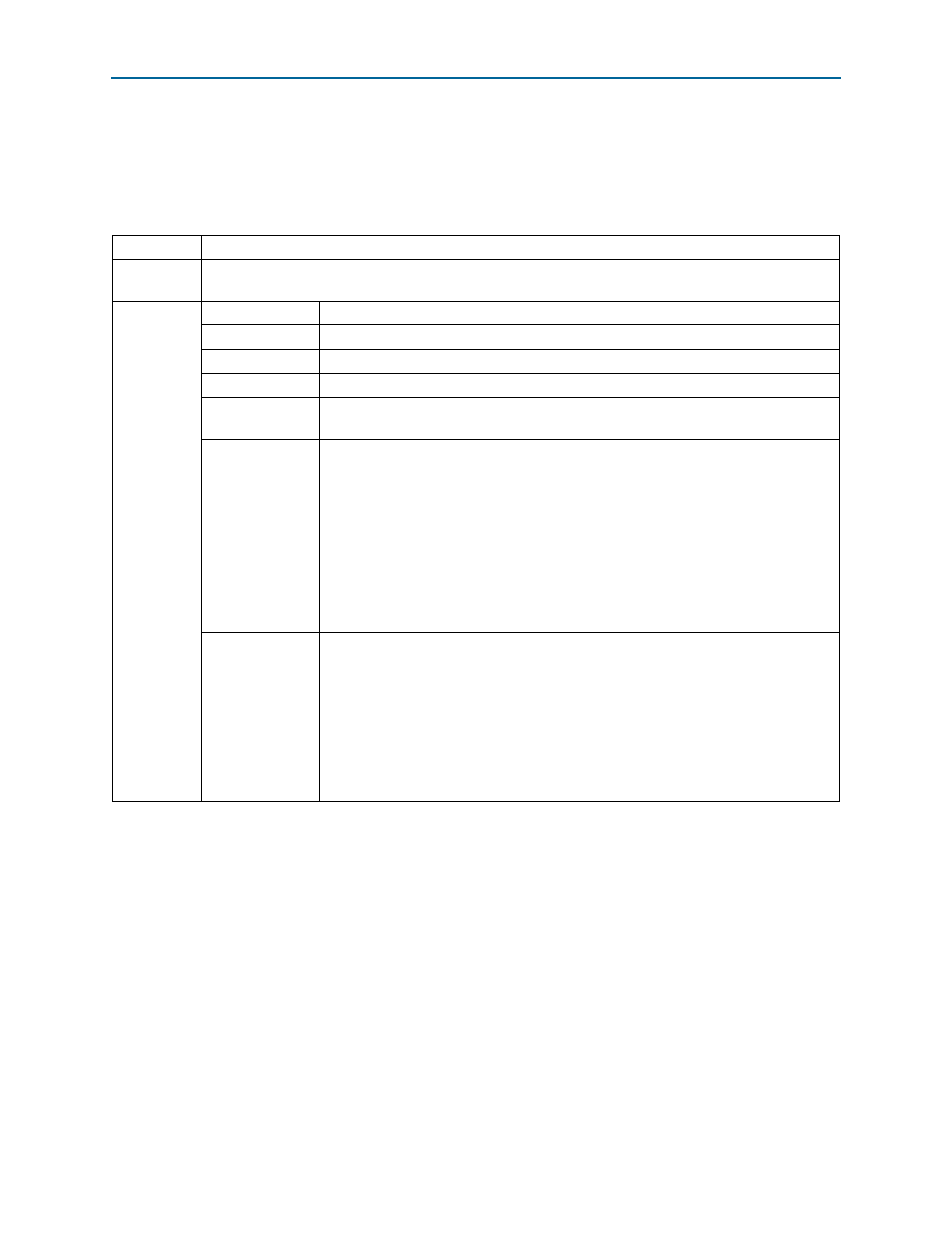

ebfm_cfgwr_imm_wait Procedure

The

ebfm_cfgwr_imm_wait

procedure writes up to four bytes of data to the specified

configuration register. This procedure waits until the write completion has been

returned.

Table 17–24.

ebfm_cfgwr_imm_wait Procedure

Location

altpcietb_bfm_driver_rp.v

Syntax

ebfm_cfgwr_imm_wait(bus_num, dev_num, fnc_num, imm_regb_ad, regb_ln, imm_data,

compl_status

Arguments

bus_num

PCI Express bus number of the target device.

dev_num

PCI Express device number of the target device.

fnc_num

Function number in the target device to be accessed.

regb_ad

Byte-specific address of the register to be written.

regb_ln

Length, in bytes, of the data written. Maximum length is four bytes. The

regb_ln

and

the

regb_ad

arguments cannot cross a DWORD boundary.

imm_data

Data to be written.

This argument is

reg [31:0]

.

The bits written depend on the length:

Length

Bits Written

4

31 downto 0

3

23 downto 0

2

5 downto 0

1

7 downto 0

compl_status

This argument is

reg [2:0]

.

This argument is the completion status as specified in the PCI Express specification:

Compl_Status Definition

000

SC— Successful completion

001

UR— Unsupported Request

010

CRS — Configuration Request Retry Status

100

CA — Completer Abort