Base address registers for function <n, Base and limit registers for root port func <n, Base address registers for function – Altera Arria V Hard IP for PCI Express User Manual

Page 60: Base and limit registers for root port func

4–8

Chapter 4: Parameter Settings for the Arria V Hard IP for PCI Express

Port Functions

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

1

When you click on a Func<n> tab, the parameter settings automatically relate to the

function currently selected.

Base Address Registers for Function <n>

describes the Base Address (BAR) register parameters.

Base and Limit Registers for Root Port Func <n>

If you specify a Root Port for function 0, the settings for Base and Limit Registers

required by Root Ports appear after the Base Address Register heading. These

settings are stored in the Type 1 Configuration Space for Root Ports. They are used for

TLP routing and specify the address ranges assigned to components that are

downstream of the Root Port or bridge. Function 0 is the only function that provides

the Root Port option for Port type.

f

For more information, refer to the

.

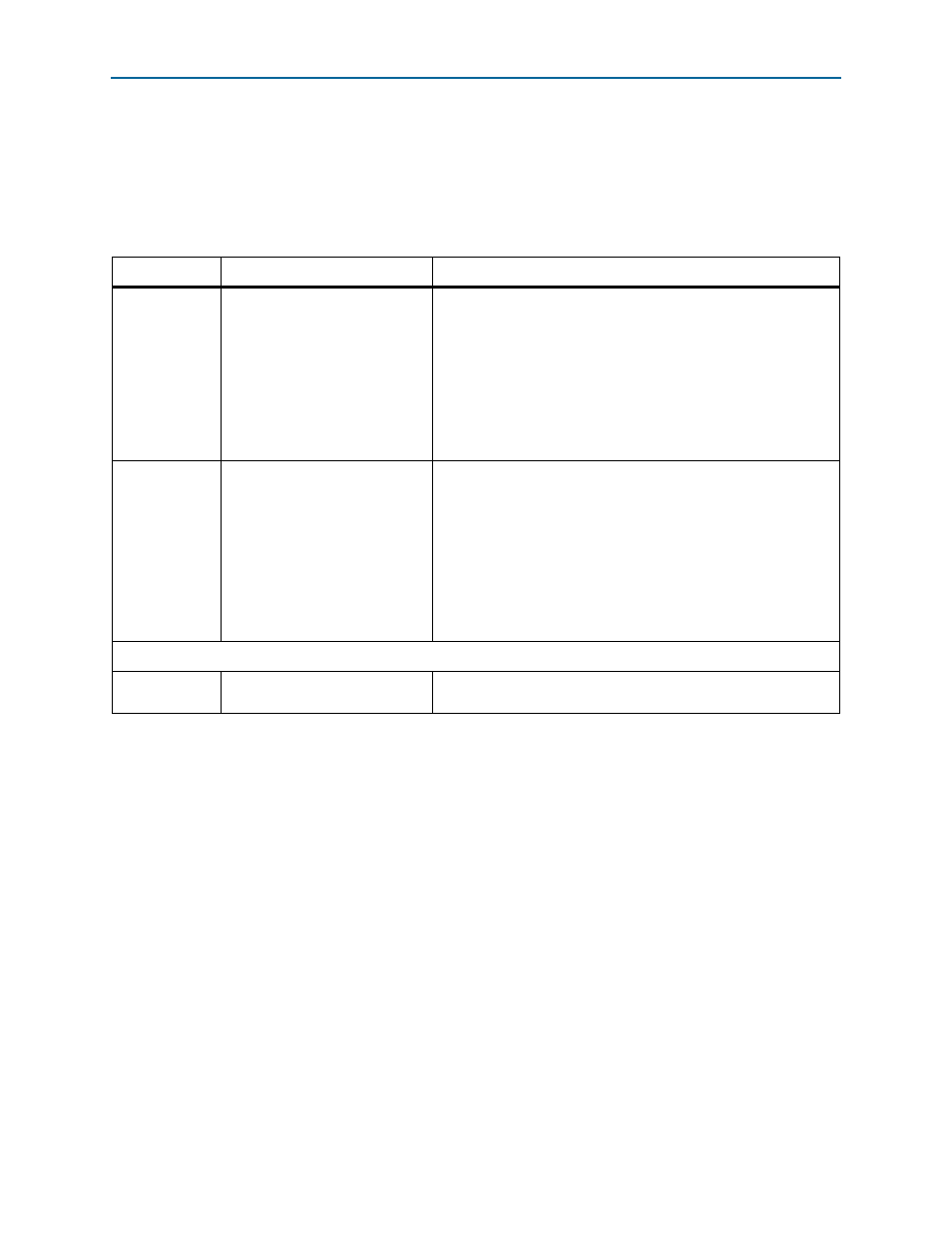

Table 4–7. Func0–Func7 BARs and Expansion ROM

Parameter

Value

Description

Type

,

,

Disabled

64-bit prefetchable memory

32-bit non-prefetchable memory

32-bit prefetchable memory

I/O address space

If you select 64-bit prefetchable memory, 2 contiguous BARs are

combined to form a 64-bit prefetchable BAR; you must set the

higher numbered BAR to Disabled. A non-prefetchable 64-bit BAR

is not supported because in a typical system, the Root Port Type 1

Configuration Space sets the maximum non-prefetchable memory

window to 32-bits. The BARs can also be configured as separate

32-bit prefetchable or non-prefetchable memories.

The I/O address space BAR is only available for the Legacy

Endpoint.

Size

16 Bytes–8 EBytes

The Endpoint and Root Port variants support the following memory

sizes:

■

×1, ×2, ×4: 128 bytes–2 GBytes or 8 EBytes

■

×8: 4 KBytes–2 GBytes or 8 EBytes (2 GBytes for 32-bit

addressing and 8 EBytes for 64-bit addressing)

The Legacy Endpoint supports the following I/O space BARs:

■

×1, ×2, ×4:16 bytes–4 KBytes

■

×8: 4 KBytes

Expansion ROM

Size

Disabled

4 KBytes–16 MBytes

Specifies the size of the optional ROM.