Example configurations, Avalon-mm interface, Configuration – Altera Embedded Peripherals IP User Manual

Page 125: Basic settings, Example configurations -3, Avalon-mm interface -3, Configuration -3, Basic settings -3

• Level-sensitive—The PIO core hardware can detect a high level. A

NOT

gate can be inserted external to

the core to provide negative sensitivity.

• Edge-sensitive—The core's edge capture configuration determines which type of edge causes an IRQ

Interrupts are individually maskable for each input port. The interrupt mask determines which input

port can generate interrupts.

Example Configurations

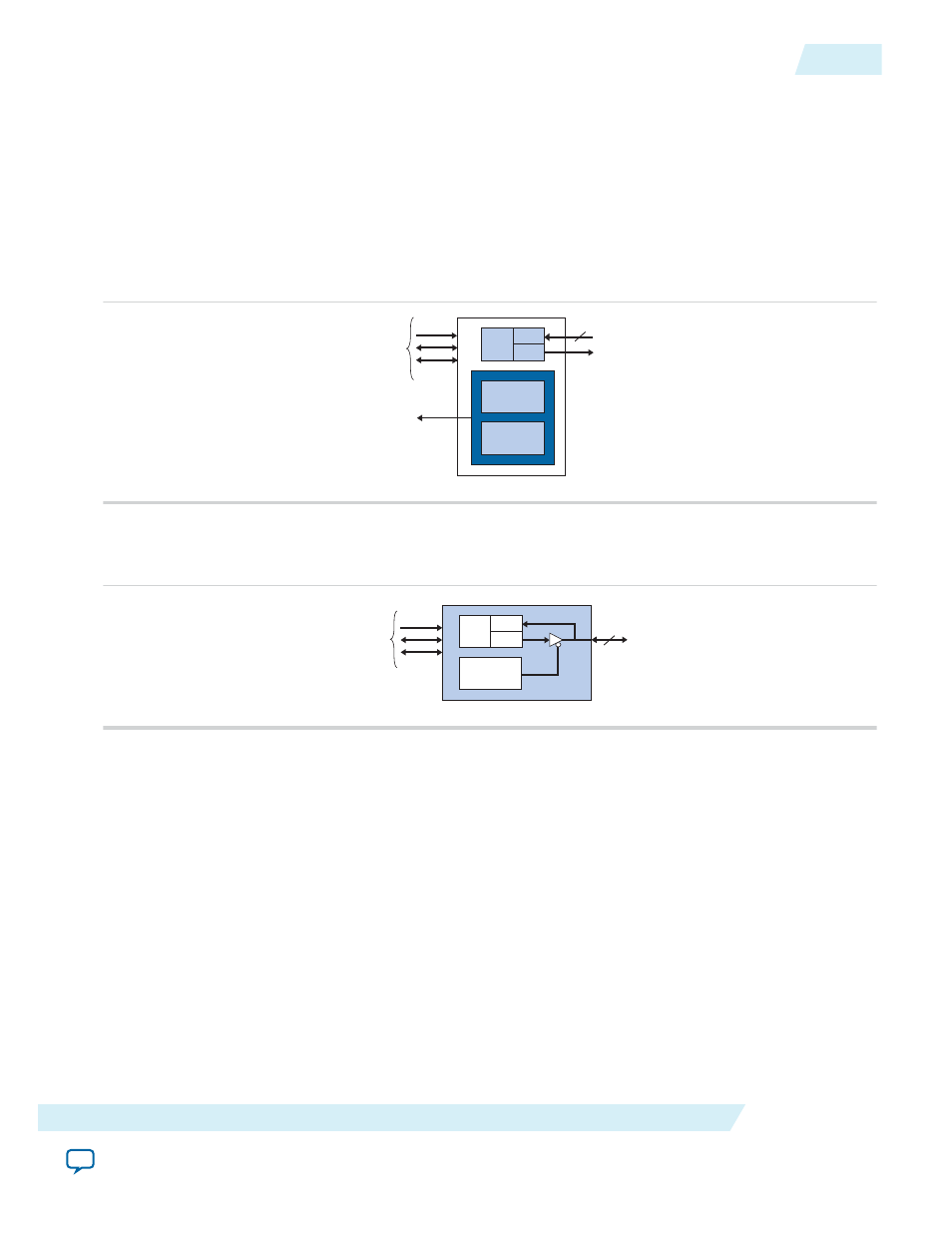

Figure 12-2: PIO Core with Input Ports, Output Ports, and IRQ Support

data

in

out

address

data

control

IRQ

32

interruptmask

edgecapture

Avalon-MM

interface

to on-chip

logic

The block diagram below shows the PIO core configured in bidirectional mode, without support for IRQs.

Figure 12-3: PIO Cores with Bidirectional Ports

direction

data

in

out

address

data

control

32

Avalon-MM

interface

to on-chip

logic

Avalon-MM Interface

The PIO core's Avalon-MM interface consists of a single Avalon-MM slave port. The slave port is capable

of fundamental Avalon-MM read and write transfers. The Avalon-MM slave port provides an IRQ output

so that the core can assert interrupts.

Configuration

The following sections describe the available configuration options.

Basic Settings

The Basic Settings page allows you to specify the width, direction and reset value of the I/O ports.

UG-01085

2014.24.07

Example Configurations

12-3

PIO Core

Altera Corporation