Parameters, Altera hal software programming model, Software files – Altera Embedded Peripherals IP User Manual

Page 280: Parameters -11, Altera hal software programming model -11, Software files -11

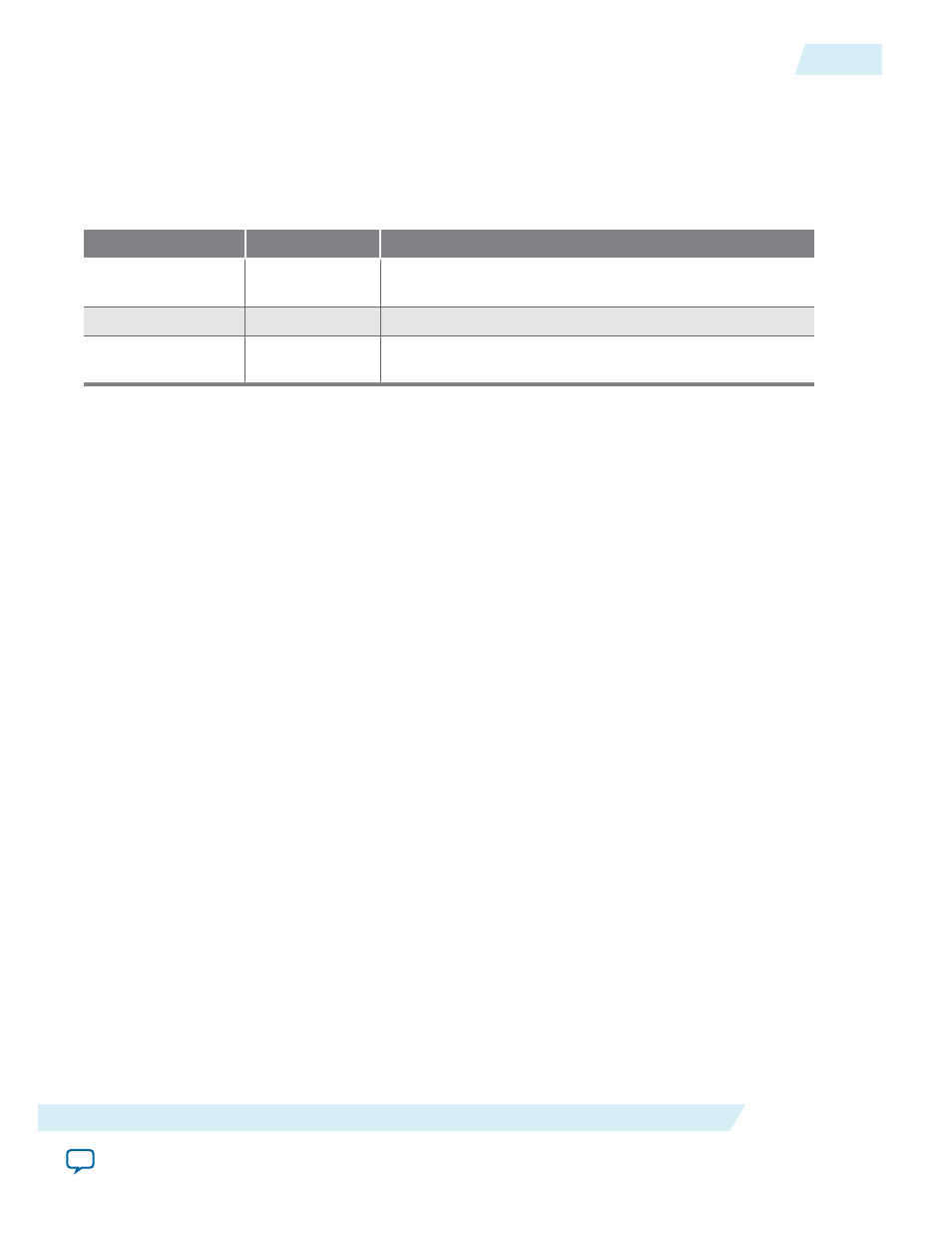

Parameters

Generation-time parameters control the features present in the hardware.The table below lists and

describes the parameters you can configure.

Table 28-10: Parameters for VIC Core

Parameter

Legal Values

Description

Number of

interrupts

1 – 32

Specifies the number of

irq_input

interrupt interfaces.

RIL width

1 – 6

Specifies the bit width of the requested interrupt level.

Daisy chain

enable

True / False

Specifies whether or not to include an input interface for

daisy chaining VICs together.

Because multiple VICs can exist in a single system, SOPC Builder assigns a unique interrupt controller

identification number to each VIC generated.

Keep the following considerations in mind when connecting the core in your SOPC Builder system:

• The CSR access interface (

csr_access

) connects to a data master port on your processor.

• The daisy chain input interface (

interrupt_controller_in)

is only visible when the daisy chain

enable option is on.

• The interrupt controller output interface (

interrupt_controller_out)

connects either to the EIC

port of your processor, or to another VIC’s daisy chain input interface (

interrupt_controller_in)

.

• For SOPC Builder interoperability, the VIC core includes an Avalon-MM master port. This master

interface is not used to access memory or peripherals. Its purpose is to allow peripheral interrupts to

connect to the VIC in SOPC Builder. The port must be connected to an Avalon-MM slave to create a

valid SOPC Builder system. Then at system generation time, the unused master port is removed during

optimization. The most simple solution is to connect the master port directly into the CSR access

interface (

csr_access

).

• SOPC Builder automatically connects interrupt sources when instantiating components. When using

the provided HAL device driver for the VIC, daisy chaining multiple VICs in a system requires that

each interrupt source is connected to exactly one VIC. You need to manually remove any extra

connections.

Altera HAL Software Programming Model

The Altera-provided driver implements a HAL device driver that integrates with a HAL board support

package (BSP) for Nios II systems. HAL users should access the VIC core via the familiar HAL API.

Software Files

The VIC driver includes the following software files. These files provide low-level access to the hardware

and drivers that integrate with the Nios II HAL BSP. Application developers should not modify these files.

UG-01085

2014.24.07

Parameters

28-11

Vectored Interrupt Controller Core

Altera Corporation