Control register, Control register -6 – Altera Embedded Peripherals IP User Manual

Page 317

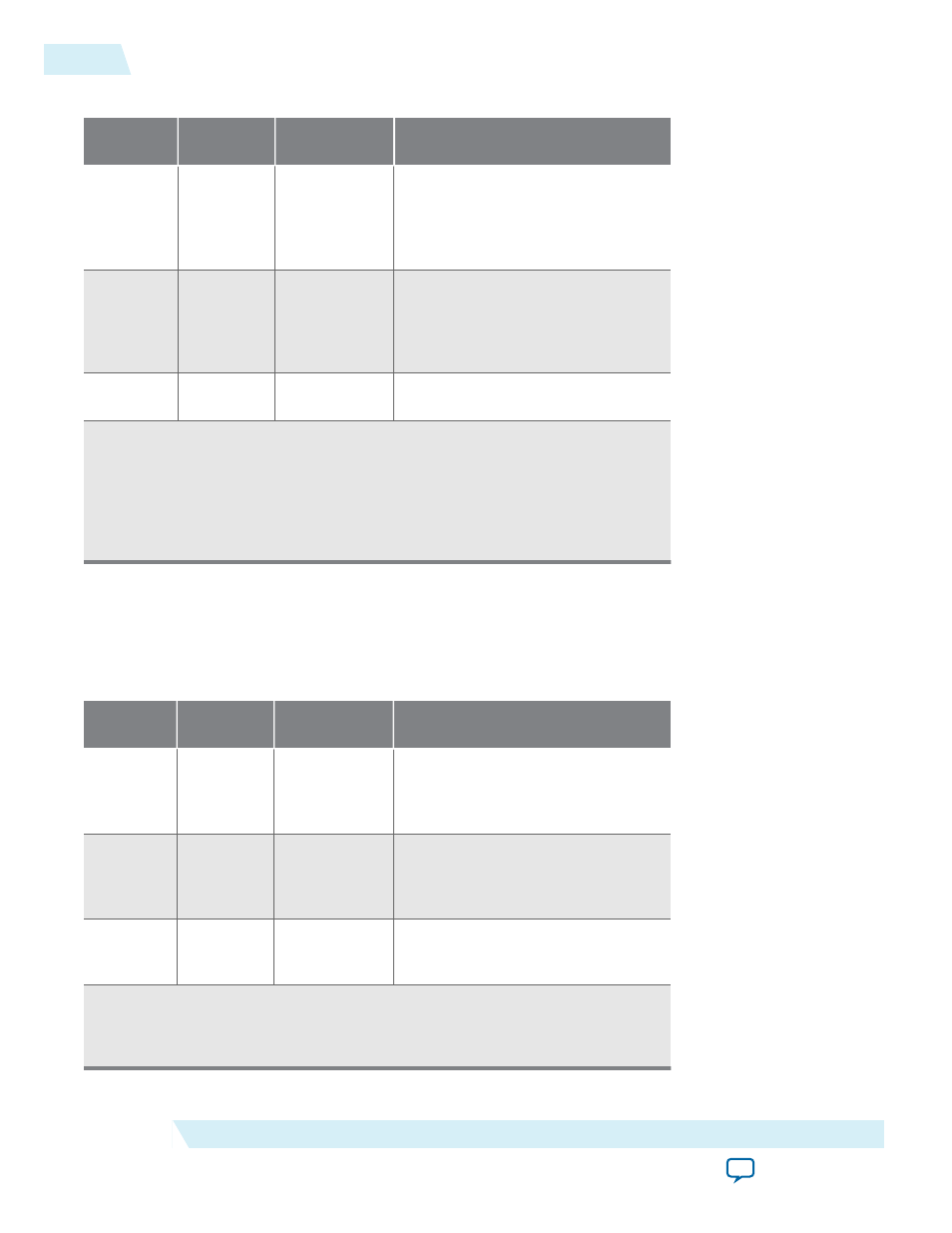

Table 32-3: Status Register Bits

Bit Number

Bit Name

Value after

reset

Description

0

locked

1

Connects to the

locked

signal on

the ALTPLL megafunction. The

locked

bit is high when valid

clocks are present on the output of

the PLL.

1

phasedone

0

Connects to the

phasedone

signal

on the ALTPLL megafunction. The

phasedone

output of the ALTPLL

is synchronized to the system

clock.

2:15/31

—

—

Reserved. Read values are

undefined.

1. The

status

register is 32-bit wide in the Avalon ALTPLL core and 16-bit

wide in the PLL core.

2. Both the

locked

and

phasedone

outputs from the Avalon ALTPLL

component are available as conduits and reflect the non-synchronized

outputs from the ALTPLL.

Control Register

Embedded software can control the PLL via the

control

register. Software can also read back the status of

control bits.

Table 32-4: Control Register Bits

Bit Number

Bit Name

Value after

reset

Description

0

areset

0

Connects to the

areset

signal on

the ALTPLL megafunction.

Writing a 1 to this bit initiates a

PLL reset.

1

pfdena

1

Connects to the

pfdena

signal on

the ALTPLL megafunction.

Writing a 0 to this bit disables the

phase frequency detection.

2:15/31

—

—

Reserved. Read values are

undefined. When writing, set

reserved bits to zero.

1. The

control

register is 32-bit wide in the Avalon ALTPLL core and 16-bit

wide in the PLL core.

32-6

Control Register

UG-01085

2014.24.07

Altera Corporation

PLL Cores