Parameter, Configuration registers, Parameter -4 – Altera Embedded Peripherals IP User Manual

Page 154: Configuration registers -4

1. Issue a write to the device register at address offset

0x21

to configure the device, port, and register

addresses of the PHY.

2. Issue a read to the

MDIO_ACCESS

register at address offset

0x20

to read the selected PHY device’s

register.

Parameter

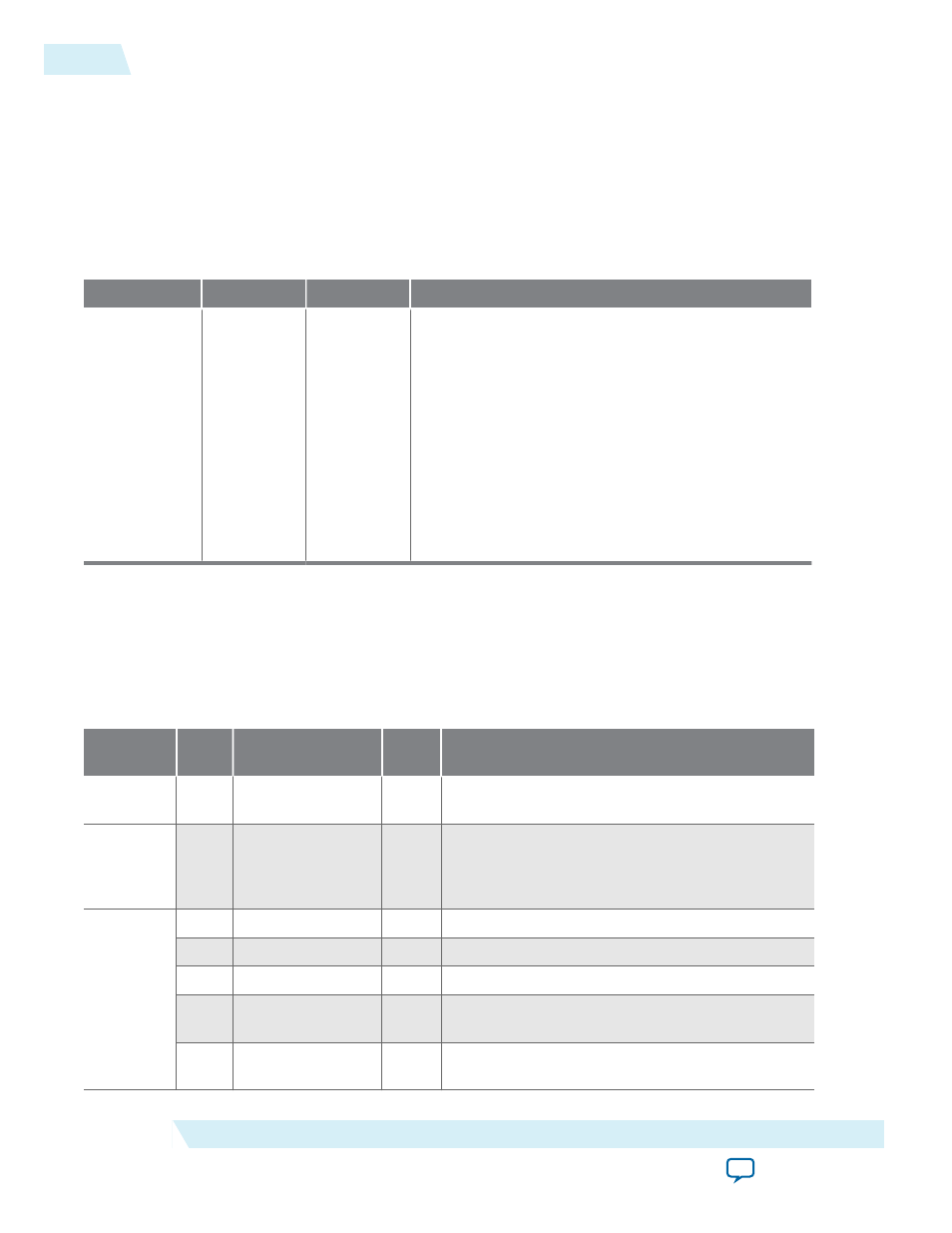

Table 15-2: Configurable Parameter

Parameter

Legal Values Default Value

Description

MDC_

DIVISOR

8-64

32

The host clock divisor provides the division factor for

the clock on the Avalon-MM interface to generate the

preferred MDIO clock (MDC). The division factor

must be defined such that the MDC frequency does

not exceed 2.5 MHz.

Formula:

For example, if the Avalon-MM interface clock

source is 100 MHz and the desired MDC frequency is

2.5 MHz, specify a value of 40 for the MDC_

DIVISOR.

Configuration Registers

An Avalon-MM master peripheral, such as a CPU, controls and communicates with the MDIO core via

32-bit registers, shown in the Register Map table.

Table 15-3: Register Map

Address

Offset

Bit(s)

Name

Access

Mode

Description

0x00-

0x1F

[31:0] Reserved

RW

Reserved for future use.

0x20

[31:0]

MDIO_ACCESS

RW

Performs a read or write of 32-bit data to the

external PHY device. The addresses of the

external PHY device’s register, device, and port

are specified in address offset

0x21

.

0x21

[4:0]

MDIO_DEVAD

RW

Contains the device address of the PHY.

[7:5]

Reserved

RW

Unused.

[12:8]

MDIO_PRTAD

RW

Contains the port address of the PHY.

[15:13

]

Reserved

RW

Unused.

[31:16

]

MDIO_REGAD

RW

Contains the register address of the PHY.

15-4

Parameter

UG-01085

2014.24.07

Altera Corporation

MDIO Core