Corresponds to irq5, For details, The interrupt enable register is set – Altera Embedded Peripherals IP User Manual

Page 278: Always returns 0

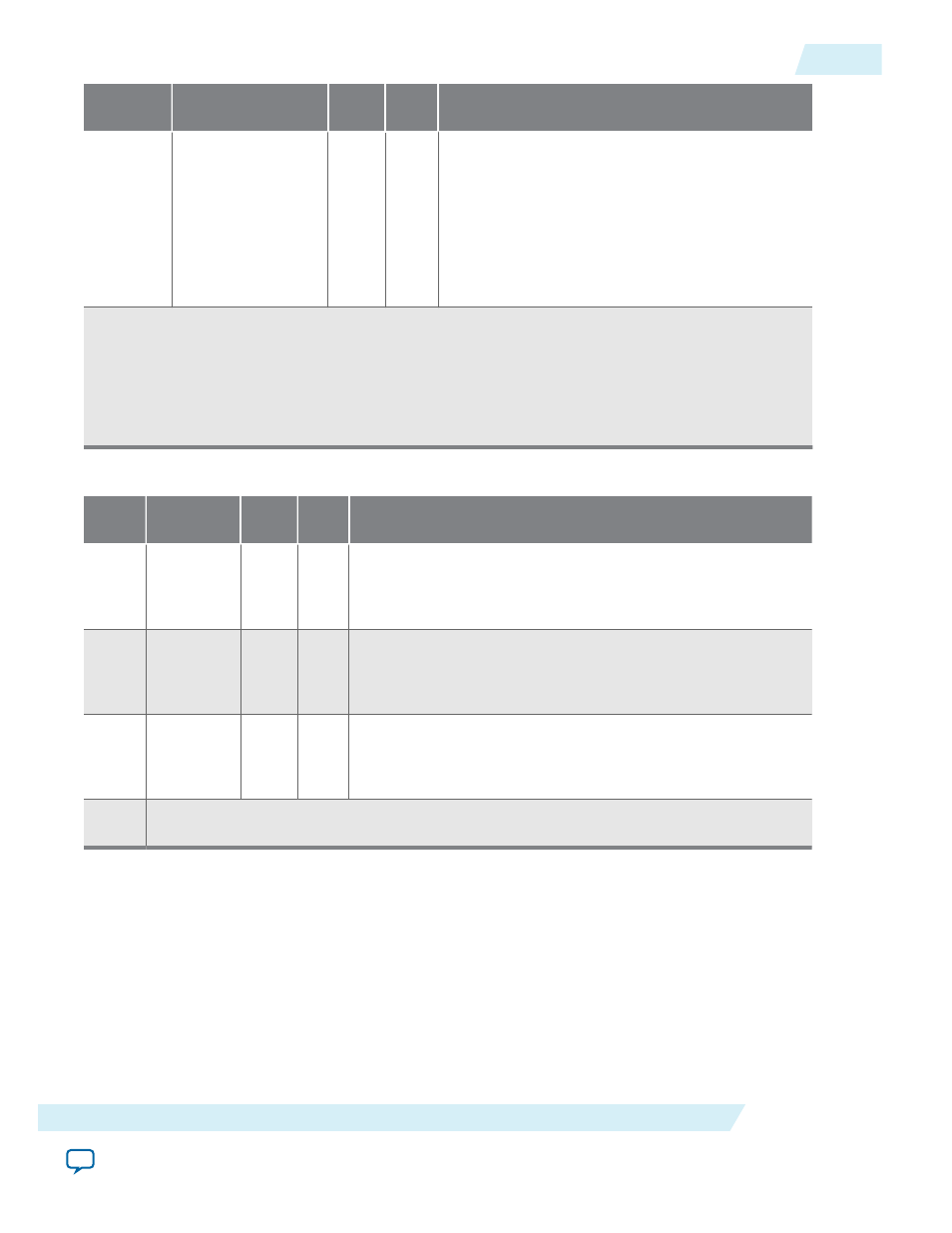

Offset

Register Name

Access Reset

Value

Description

43

VEC_TBL_ADDR

R

0

The vector table address register.

VEC_TBL_ADDR

provides the RHA for the IRQ value with the

highest priority pending interrupt. If no interrupt

is active, the value in this register is 0.

If daisy chain input is enabled and is the highest

priority interrupt, the vector table address

register contains the RHA value from the daisy

chain input interface.

1. This register contains a 1-bit field for each of the 32 interrupt inputs. When the VIC is

configured for less than 32 interrupts, the corresponding 1-bit field for each unused interrupts

is tied to zero. Reading these locations always returns 0, and writing is ignored. To determine

which interrupts are present, write the value 0xffffffff to the register and then read the register

contents. Any bits that return zero do not have an interrupt present.

Table 28-7: The INT_CONFIG Register Map

Bits

Field Name Access Reset

Value

Description

0:5

RIL

R/W

0

The requested interrupt level field.

RIL

contains the interrupt

level of the interrupt requesting service. The processor can use

the value in this field to determine if the interrupt is of higher

priority than what the processor is currently doing.

6

RNMI

R/W

0

The requested non-maskable interrupt field.

RNMI

contains the

non-maskable interrupt mode of the interrupt requesting

service. When 0, the interrupt is maskable. When 1, the

interrupt is non-maskable.

7:12

RRS

R/W

0

The requested register set field.

RRS

contains the number of

the processor register set that the processor should use for

processing the interrupt. Software must ensure that only

register values supported by the processor are used.

13:3

1

Reserved

For expanded definitions of the terms in the INT_CONFIG Register Map table, refer to the

chapter of the Nios II Software Developer’s Handbook.

UG-01085

2014.24.07

Register Maps

28-9

Vectored Interrupt Controller Core

Altera Corporation