Document revision history, Document revision history -16 – Altera Embedded Peripherals IP User Manual

Page 150

1. Set the initialization parameters, which are defined in the master transactor model source code.

These parameters control the address space reserved by the target transactor model and other

PCI agents on the PCI bus.

2. The master transactor defines the tasks (Verilog HDL) needed to initiate PCI transactions in

your testbench. Add the commands that correspond to the transactions you want to implement

in your tests to the master transactor model source code. At a minimum, you must add configu‐

ration commands to set the BAR for the target transactor model and write the configuration

space of the PCI Lite core. Additionally, you can add commands to initiate memory or I/O

transactions to the PCI Lite core.

3. Compile the files in your simulator, including the testbench modules and the files created by

SOPC Builder.

4. Simulate the testbench for the desired time period.

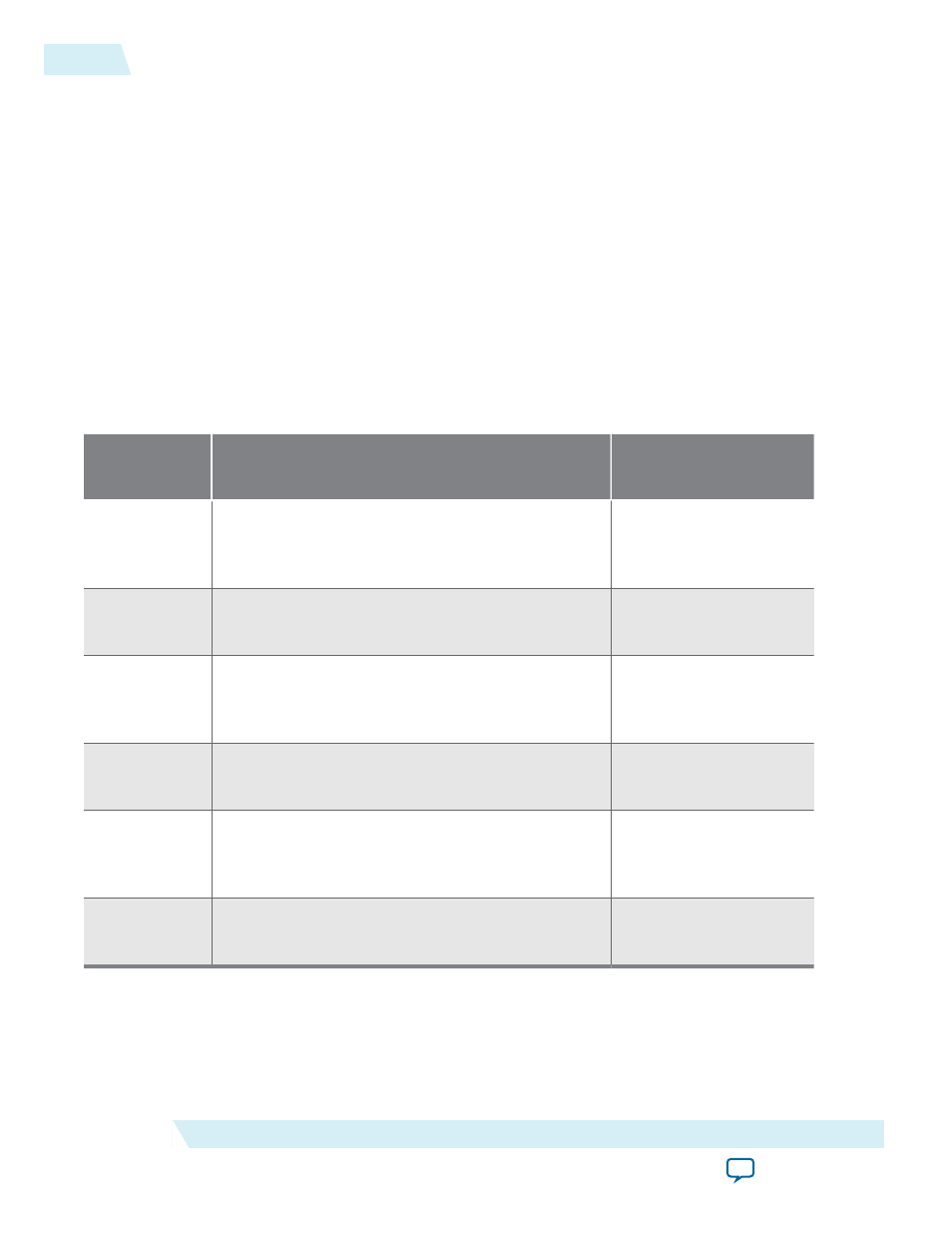

Document Revision History

Table 14-10: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

December

2010

v10.1.0

Removed the “Device Support”, “Instantiating the Core

in SOPC Builder”, and “Referenced Documents”

sections.

—

July 2010

v10.0.0

No change from previous release.

November

2009

v9.1.0

No change from previous release.

—

March 2009

v9.0.0

No change from previous release.

—

November

2008

v8.1.0

Changed to 8-1/2 x 11 page size. Edited the command

errors in the Simulation Flow section.

—

May 2008

v8.0.0

Initial release.

—

14-16

Document Revision History

UG-01085

2014.24.07

Altera Corporation

PCI Lite Core