Synchronizer stages, Flow control, Streaming data (dma) control – Altera Embedded Peripherals IP User Manual

Page 74

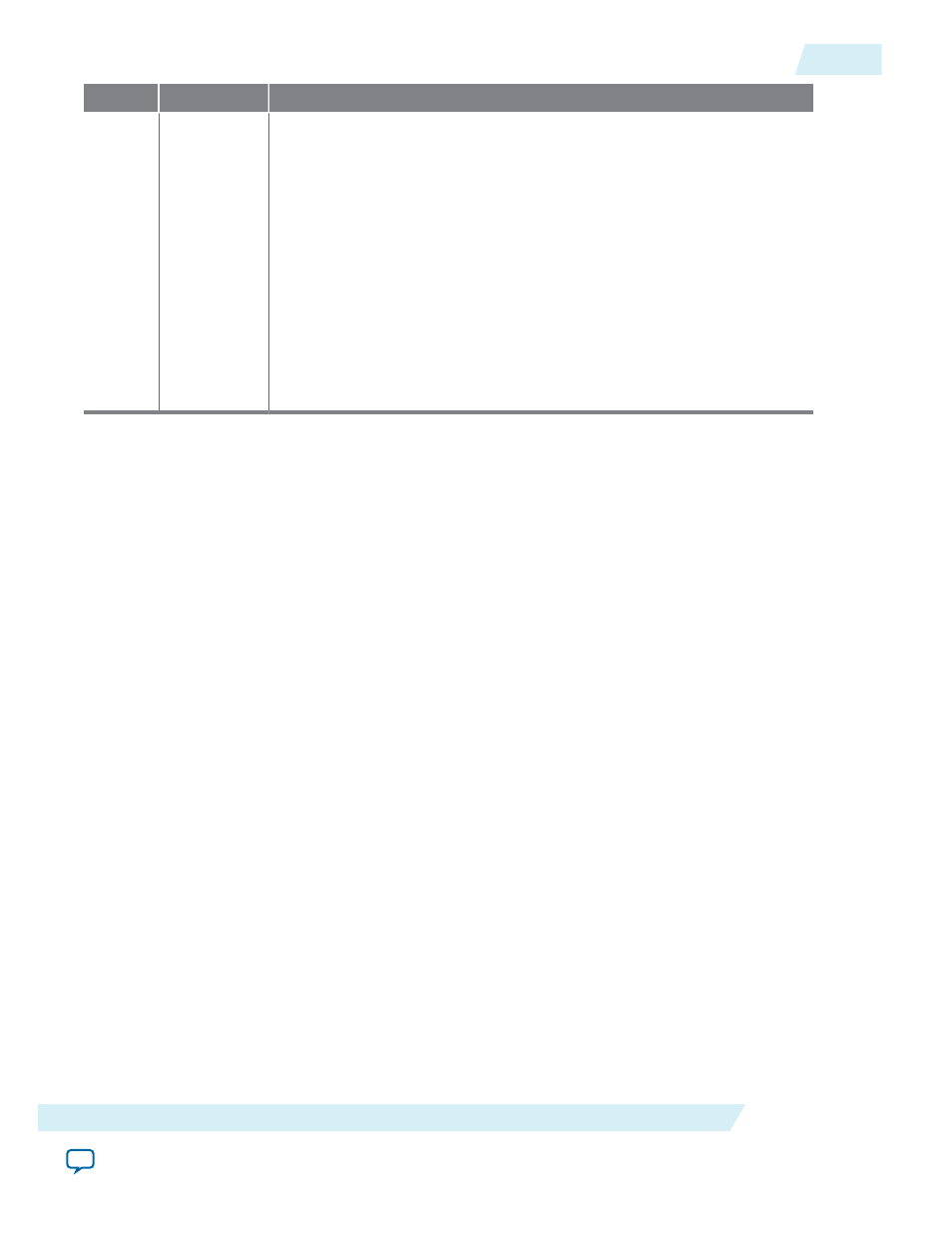

Setting

Legal Values

Description

Parity None, Even,

Odd

This setting determines whether the UART core transmits characters with

parity checking, and whether it expects received characters to have parity

checking.

When Parity is set to None, the transmit logic sends data without

including a parity bit, and the receive logic presumes the incoming data

does not include a parity bit. The

PE

bit in the

status

register is not

implemented; it always reads 0.

When Parity is set to Odd or Even, the transmit logic computes and

inserts the required parity bit into the outgoing TXD bitstream, and the

receive logic checks the parity bit in the incoming RXD bitstream. If the

receiver finds data with incorrect parity, the

PE

bit in the

status

register is

set to 1. When Parity is Even, the parity bit is 0 if the character has an

even number of 1 bits; otherwise the parity bit is 1. Similarly, when parity

is Odd, the parity bit is 0 if the character has an odd number of 1 bits.

Synchronizer Stages

The option Synchronizer Stages allows you to specify the length of synchronization register chains. These

register chains are used when a metastable event is likely to occur and the length specified determines the

meantime before failure. The register chain length, however, affects the latency of the core.

For more information on metastability in Altera devices, refer to

For more information on metastability analysis and synchronization register chains, refer to the

Quartus II Handbook.

Flow Control

When the option Include CTS/RTS pins and control register bits is turned on, the UART core includes

the following features:

•

cts_n

(logic negative CTS) input port

•

rts_n

(logic negative RTS) output port

•

CTS

bit in the

status

register

•

DCTS

bit in the

status

register

•

RTS

bit in the

control

register

•

IDCTS

bit in the

control

register

Based on these hardware facilities, an Avalon-MM master peripheral can detect CTS and transmit RTS

flow control signals. The

CTS

input and

RTS

output ports are tied directly to bits in the

status

and

control

registers, and have no direct effect on any other part of the core. When using flow control, be

sure the terminal program on the host side is also configured for flow control.

When the Include CTS/RTS pins and control register bits setting is off, the core does not include the

aforementioned hardware and continuous writes to the UART may loose data. The control/status bits

CTS

,

DCTS

,

IDCTS

, and

RTS

are not implemented; they always read as 0.

Streaming Data (DMA) Control

The UART core's Avalon-MM interface optionally implements Avalon-MM transfers with flow control.

Flow control allows an Avalon-MM master peripheral to write data only when the UART core is ready to

UG-01085

2014.24.07

Synchronizer Stages

8-5

UART Core

Altera Corporation