Control register – Altera Embedded Peripherals IP User Manual

Page 83

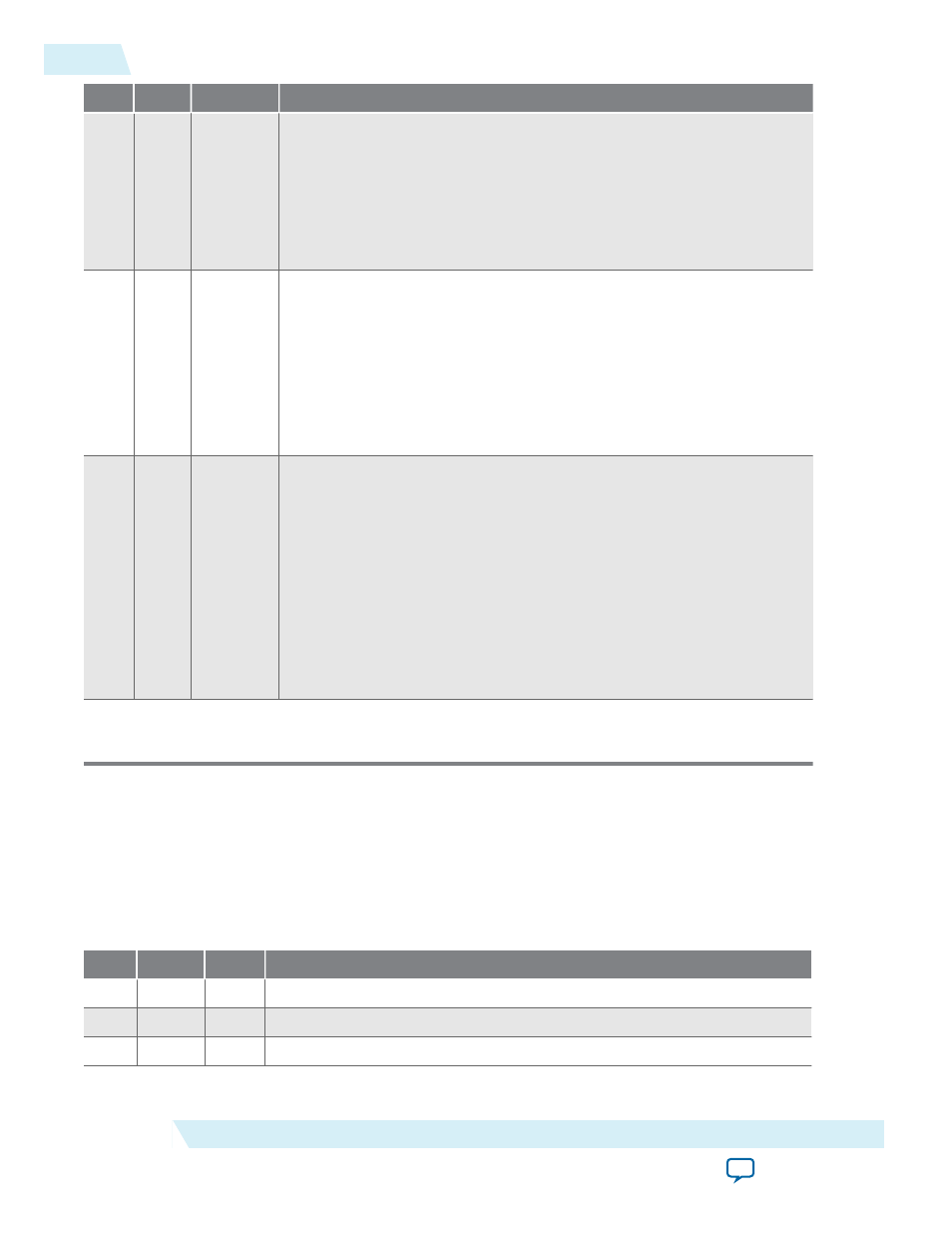

Bit

Name

Access

Description

10

(1

)

DCTS

RC

Change in clear to send (CTS) signal. The

DCTS

bit is set to 1 whenever a

logic-level transition is detected on the

CTS_N

input port (sampled

synchronously to the Avalon-MM clock). This bit is set by both falling

and rising transitions on

CTS_N

. The

DCTS

bit stays set to 1 until it is

explicitly cleared by a write to the

status

register.

If the Flow Control hardware option is not enabled, the

DCTS

bit always

reads 0. Refer to the Flow Control section.

11

(1

)

CTS

R

Clear-to-send (CTS) signal. The

CTS

bit reflects the

CTS_N

input’s

instantaneous state (sampled synchronously to the Avalon-MM clock).

The

CTS_N

input has no effect on the transmit or receive processes. The

only visible effect of the

CTS_N

input is the state of the

CTS

and

DCTS

bits,

and an IRQ that can be generated when the control register’s idcts bit is

enabled.

If the Flow Control hardware option is not enabled, the

CTS

bit always

reads 0. Refer to the Flow Control section.

12

(1

)

EOP

R

(1)

End of packet encountered. The

EOP

bit is set to 1 by one of the following

events:

An EOP character is written to

txdata

An EOP character is read from

rxdata

The EOP character is determined by the contents of the

endofpacket

register. The

EOP

bit stays set to 1 until it is explicitly cleared by a

write

to the

status

register.

If the Include End-of-Packet Register hardware option is not enabled,

the

EOP

bit always reads 0. Refer to Streaming Data (DMA) Control

Section.

Note

:

1. This bit is optional and may not exist in hardware.

control Register

The

control

register consists of individual bits, each controlling an aspect of the UART core's operation.

The value in the

control

register can be read at any time.

Each bit in the

control

register enables an IRQ for a corresponding bit in the

status

register. When both

a status bit and its corresponding interrupt-enable bit are 1, the core generates an IRQ.

Table 8-8: control Register Bits

Bit

Name

Access

Description

0

IPE

RW

Enable interrupt for a parity error.

1

IFE

RW

Enable interrupt for a framing error.

2

IBRK

RW

Enable interrupt for a break detect.

8-14

control Register

UG-01085

2014.24.07

Altera Corporation

UART Core