Registers of component, Status register, Registers of component -3 – Altera Embedded Peripherals IP User Manual

Page 322

When a new message data is written into Altera MSI-to-GIC Generator module, the storage word

associated Status bit is set automatically and a level interrupt output is then fired. The host processor that

receives this interrupt output is required to service the MSI request, as indicated in the following

procedure:

1. The host processor reads the Status Register to recognize which data word location of its storage is

causing the interrupt.

2. The host processor reads the firing data word location for its system-specified message data value sent

by the MSI capable function. Upon reading the data word, message data is considered consumed, the

associated Status bit is then unset automatically. If the word location entry is empty, then the Status bit

still remains asserted.

3. The host processor services either the MSI sender or the function who calls for the MSI.

4. Upon completing the interrupt service for the first entry, the host processor may continue to service

the remaining entry if there is any residing inside the word location, by observing the associated Status

bit.

5. The host processor may run through the Status Register and service each firing Status bit in any order.

Registers of Component

The following table illustrates the Altera MSI-to-GIC Generator registers map as observed by the host

processor from its Avalon-MM CSR interfaces. The bit size of each register is numbered according to the

configured number of data word storage for MSI message of the component. The maximum width of each

register should be 32 bits because the configurable value range is from 1 to 32.

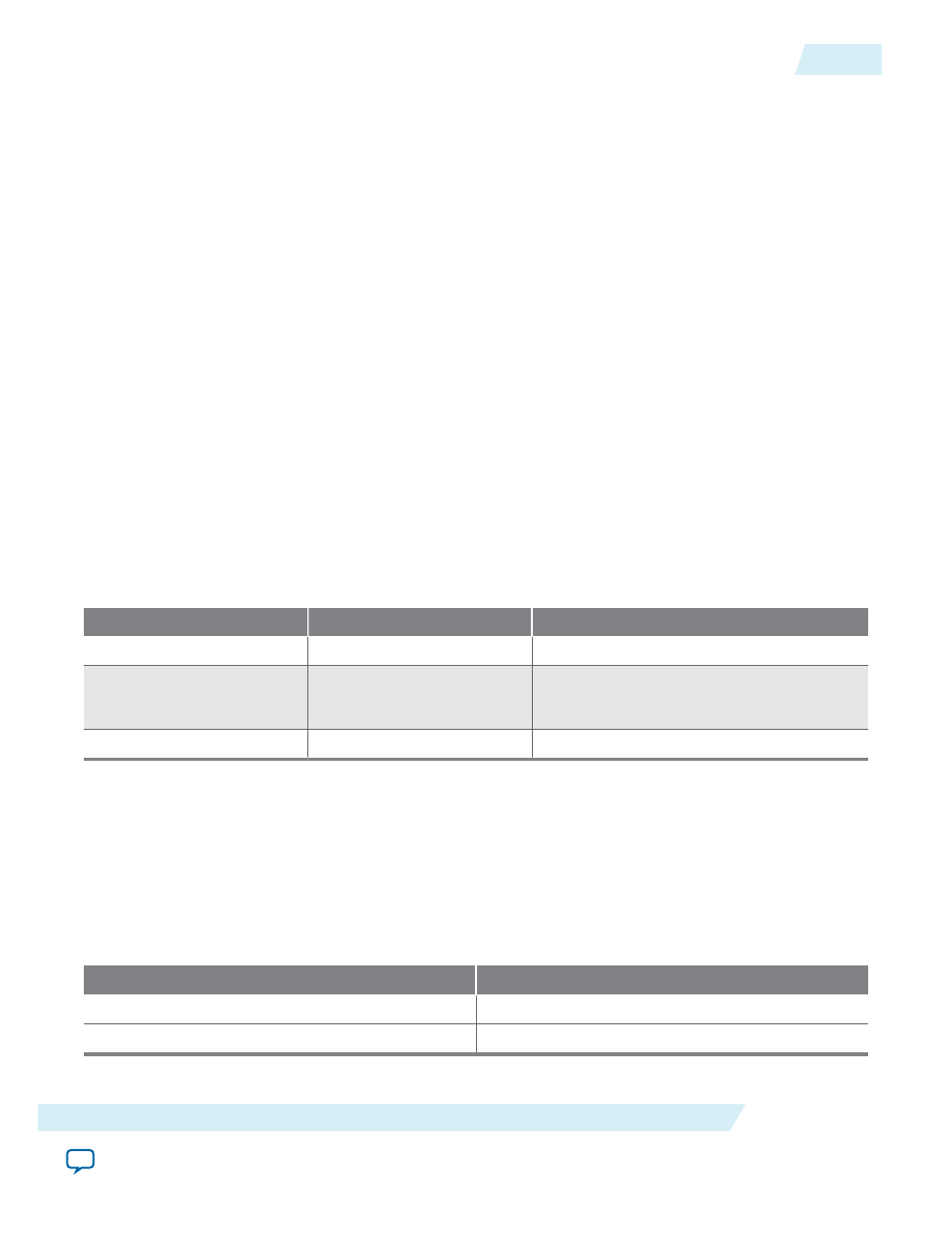

Table 33-1: CRA registers map

Word Address Offset

Register/ Queue Name

Attribute

0x0

Status register

R

0x1

Error register

RW

Note: Write '1' to clear

0x2

Interrupt Mask register

RW

Status Register

The status register contains individual bits representing each of the data words location entry status. An

unread entry sets the Status bit. The Status bit is cleared automatically when entry is empty. The value of

the register is defaulted to ‘0’ upon reset.

The following table illustrates the Status register field.

Table 33-2: Status Register fields

Field Name

Bit Location

Status bit for message data word location [31:1]

31:1

Status bit for message data word location [0]

0

UG-01085

2014.24.07

Registers of Component

33-3

Altera MSI to GIC Generator

Altera Corporation