Pci timing constraint files, Pci timing constraint files -12 – Altera Embedded Peripherals IP User Manual

Page 146

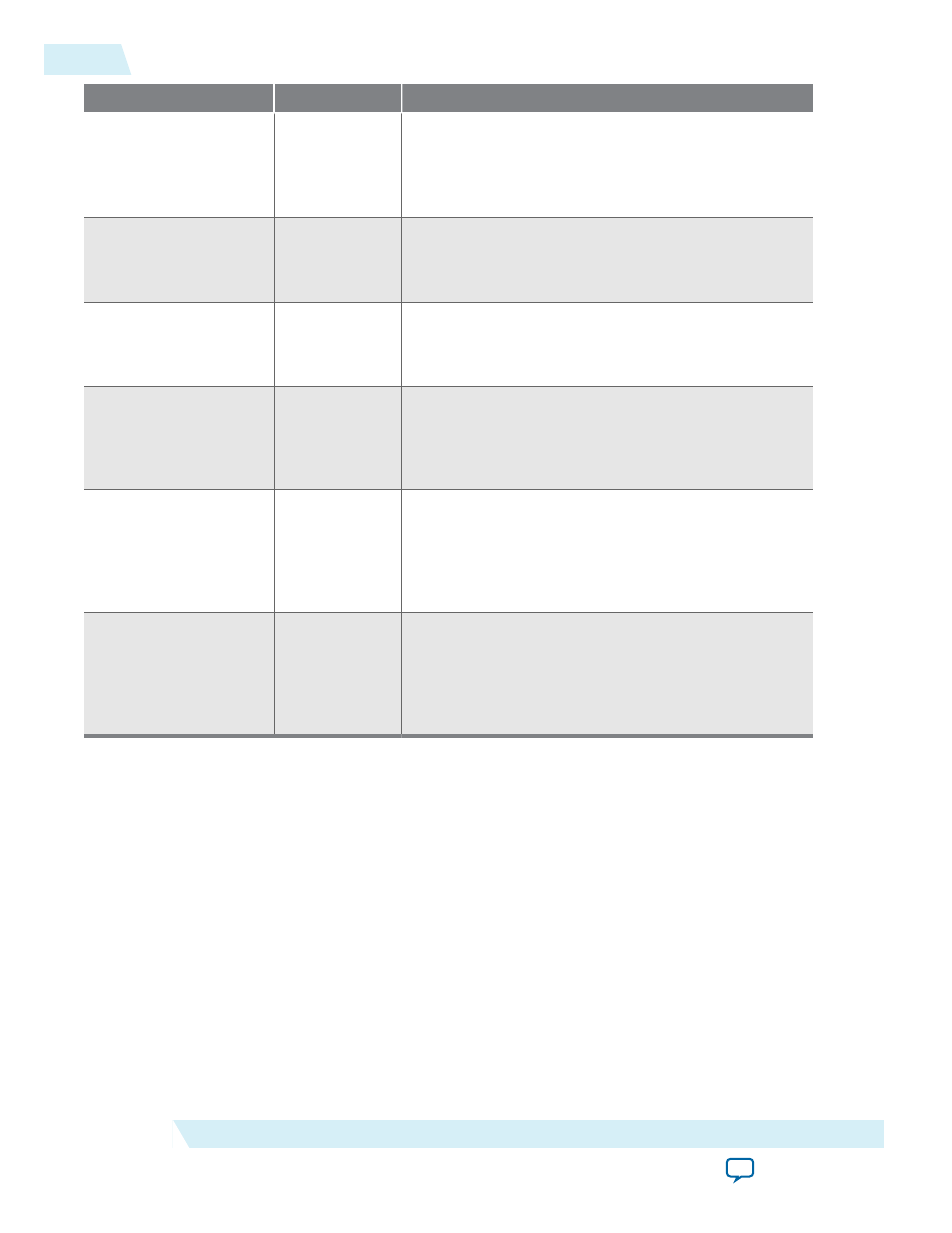

Parameters

Legal Values

Description

Class Code

<register value> Class code register. This parameter is a 24-bit hexadec‐

imal value that sets the class code register in the

configuration space. The value entered for this

parameter must be valid PCI SIG-assigned class code

register value.

Revision ID

<register value> Revision ID register. This parameter is an 8-bit read-

only register that identifies the revision number of the

device. The value of this register is assigned by the

manufacturer.

Subsystem ID

<register value> Subsystem ID register. This parameter is a 16-bit

hexadecimal value that sets the subsystem ID register

in the PCI configuration space. Any value can be

entered for this parameter.

Subsystem Vendor

ID

<register value> Subsystem vendor ID register. This parameter is a 16-

bit hexadecimal value that sets the subsystem vendor

ID register in the PCI configuration space. The value

for this parameter must be a valid PCI SIG-assigned

vendor ID number.

Maximum Latency

<register value> Maximum latency register. This parameter is an 8-bit

hexadecimal value that sets the maximum latency

register in the configuration space. This parameter

must be set according to the guidelines in the PCI

specifications. Only meaningful when the Enable

Master/Target Mode option is turned On.

Minimum Grant

<register value> Minimum grant register. This parameter is an 8-bit

hexadecimal value that sets the minimum grant

register in the PCI configuration space. This parameter

must be set according to the guidelines in the PCI

specifications. Only meaningful when the Enable

Master/Target Mode option is turned On.

PCI Timing Constraint Files

The PCI Lite core supplies a Tcl timing constraint file for your target device family.

When run, the constraint file automatically sets the PCI Lite core assignments for your design such as PCI

Lite core hierarchy, device family, density and package type used in your Quartus II project.

To run a PCI constraint file, perform the following steps:

1. Copy pci_constraints.tcl from <quartus_root>/ip/sopc_builder_ip/altera_avalon_pci_lite.

2. Update the pin list in the Tcl constraint file. Edit the

get_user_pin_name

procedure in the Tcl

constraint file to match the default pin names. To edit the PCI constraint file, follow these steps:

a. Locate the

get_user_pin_name

procedure. This procedure maps the default PCI pin names to user

PCI pin names. The following lines are the first few lines of the procedure:

proc get_user_pin_name { internal_pin_name } {

14-12

PCI Timing Constraint Files

UG-01085

2014.24.07

Altera Corporation

PCI Lite Core