Dma descriptors, Dma descriptors -13 – Altera Embedded Peripherals IP User Manual

Page 204

Altera recommends that you read the status register only after the

RUN

bit in the

control

register is

cleared.

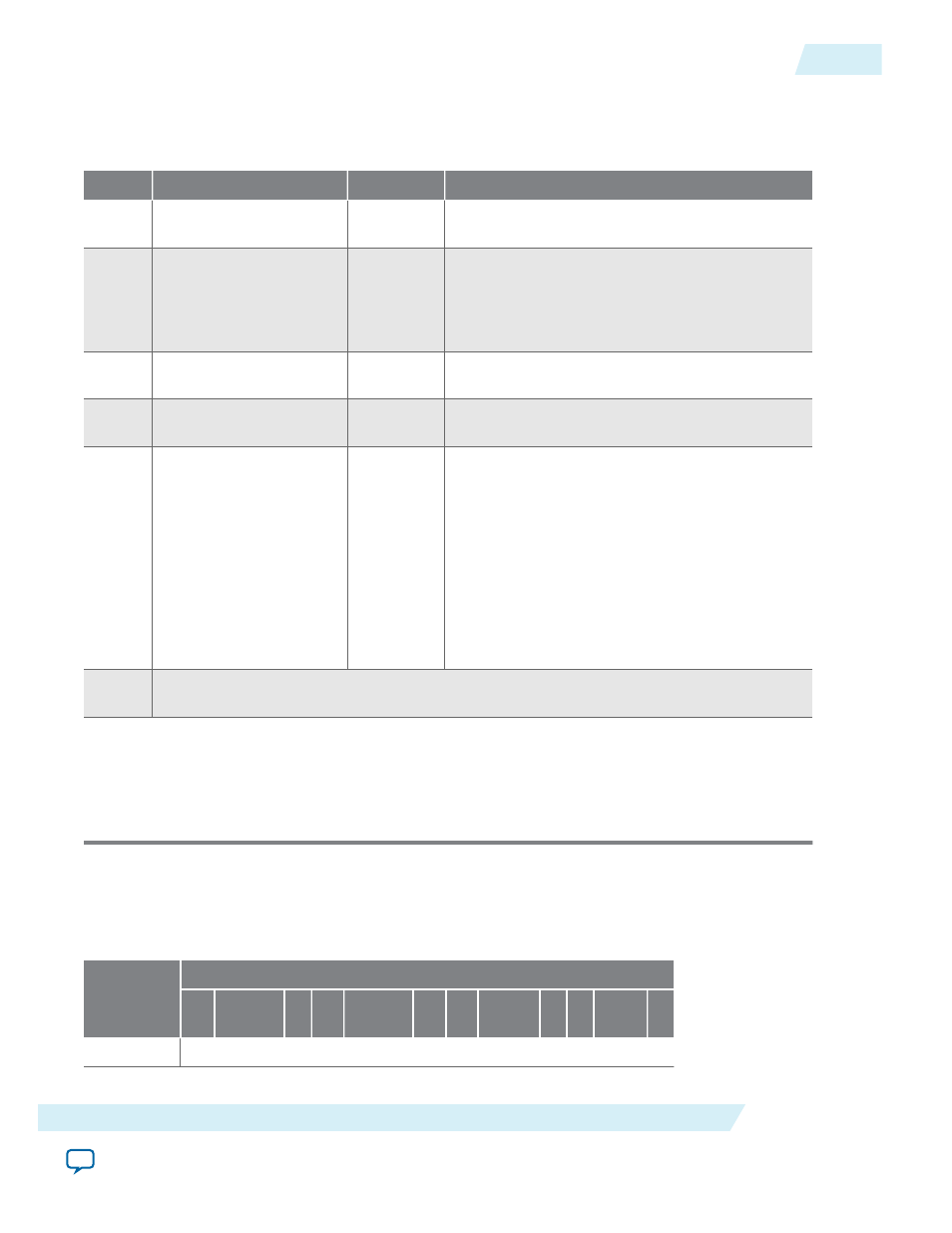

Table 21-8: Status Register Bit Map

Bit

Bit Name

Access

Description

0

ERROR

R/C

A value of 1 indicates that an Avalon-ST error

was encountered during a transfer.

1

EOP_ENCOUNTERED

R/C

A value of 1 indicates that the transfer was

terminated by an end-of-packet (EOP) signal

generated on the Avalon-ST source interface.

This condition is only possible in stream-to-

memory configurations.

2

DESCRIPTOR_COMPLETED

R/C

A value of 1 indicates that a descriptor was

processed to completion.

3

CHAIN_COMPLETED

R/C

A value of 1 indicates that the core has

completed processing the descriptor chain.

4

BUSY

R

A value of 1 indicates that descriptors are being

processed. This bit is set to 1 on the next clock

cycle after the

RUN

bit is asserted and does not

get cleared until one of the following event

occurs:

Descriptor processing completes and the

RUN

bit

is cleared.

An error condition occurs, the

STOP_DMA_ER

bit

is set to 1 and the processing of the current

descriptor completes.

5 ..

31

Reserved

1. This bit must be cleared after a read is performed. Write one to clear this bit.

2. This bit is updated by hardware after each DMA transfer completes. It remains set until

software writes one to clear.

3. This bit is continuously updated by the hardware.

DMA Descriptors

See the Data Structure section for the structure definition.

Table 21-9: DMA Descriptor Structure

Byte Offset

Field Names

31

2

4

23

16 15

8 7

0

base

source

UG-01085

2014.24.07

DMA Descriptors

21-13

Scatter-Gather DMA Controller Core

Altera Corporation