Altera Embedded Peripherals IP User Manual

Page 205

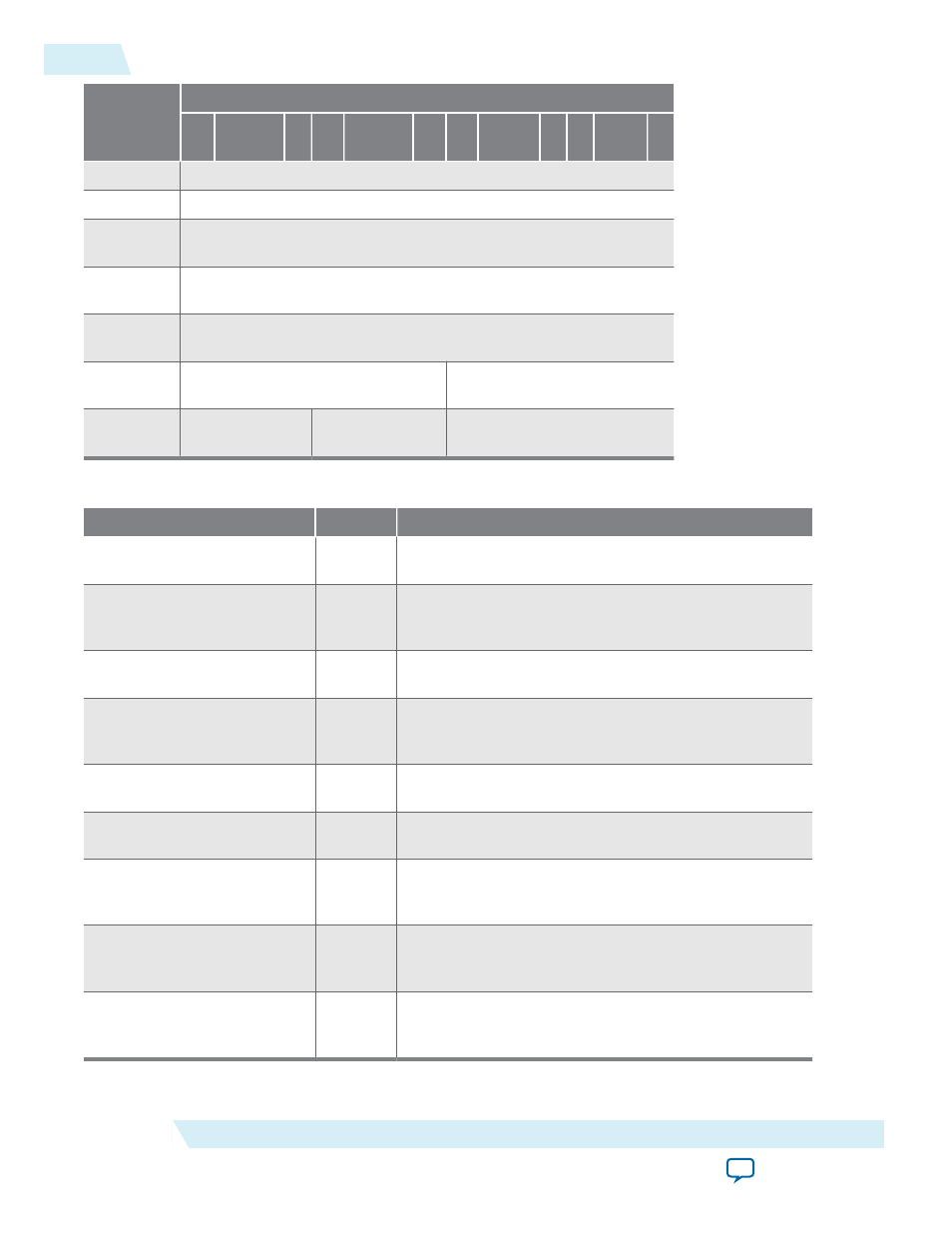

Byte Offset

Field Names

31

2

4

23

16 15

8 7

0

base + 4 Reserved

base + 8

destination

base +

12

Reserved

base +

16

next_desc_ptr

base +

20

Reserved

base +

24

Reserved

bytes_to_transfer

base +

28

desc_control

desc_status

actual_bytes_

transferred

Table 21-10: DMA Descriptor Field Description

Field Name

Access

Description

source

R/W

Specifies the address of data to be read. This address is

set to 0 if the input interface is an Avalon-ST interface.

destination

R/W

Specifies the address to which data should be written.

This address is set to 0 if the output interface is an

Avalon-ST interface.

next_desc_ptr

R/W

Specifies the address of the next descriptor in the linked

list.

bytes_to_transfer

R/W

Specifies the number of bytes to transfer. If this field is

0, the SG-DMA controller core continues transferring

data until it encounters an EOP.

read_

R/W

Specifies the burst length in bytes for a burst read from

Avalon devices (memory).

write_

R/W

Specifies the burst length in bytes for a burst write to

Avalon devices (memory).

actual_bytes_

transferred

R

Specifies the number of bytes that are successfully

transferred by the core. This field is updated after the

core processes a descriptor.

desc_status

R/W

This field is updated after the core processes a

descriptor. See DESC_STATUS Bit Map for the bit

map of this field.

desc_control

R/W

Specifies the behavior of the core. This field is updated

after the core processes a descriptor. See the DESC_

CONTROL Bit Map table for descriptions of each bit.

21-14

DMA Descriptors

UG-01085

2014.24.07

Altera Corporation

Scatter-Gather DMA Controller Core