Default settings for rrs and ril, Vic bsp design rules for altera hal implementation – Altera Embedded Peripherals IP User Manual

Page 291

Default Settings for RRS and RIL

The default assignment of RRS and RIL values for each interrupt assumes interrupt port 0 on the VIC

instance attached to your processor is the highest priority interrupt, with successively lower priorities as

the interrupt port number increases. Interrupt ports on other VIC instances connected through the first

VIC's daisy chain interface are assigned successively lower priorities.

To make effective use of the VIC interrupt setting defaults, assign your highest priority interrupts to low

interrupt port numbers on the VIC closest to the processor. Assign lower priority interrupts and

interrupts that do not need exclusive access to a shadow register set, to higher interrupt port numbers, or

to another daisy-chained VIC.

The following steps describe the algorithm for default RIL assignment:

1. The formula 2

RIL width

-1 is used to calculate the maximum RIL value.

2. interrupt port 0 on the VIC connected to the processor is assigned the highest possible RIL.

3. The RIL value is decremented and assigned to each subsequent interrupt port in succession until the

RIL value is 1.

4. The RILs for all remaining interrupt ports on all remaining VICs in the chain are assigned 1.

The following steps describe the algorithm for default RRS assignment:

5. The highest register set number is assigned to the interrupt with the highest priority.

6. Each subsequent interrupt is assigned using the same method as the default RIL assignment.

For example, consider a system with two VICs, VIC0 and VIC1. Each VIC has an RIL width of 3, and

each has 4 interrupt ports. VIC0 is connected to the processor and VIC1 to the daisy chain interface on

VIC0. The processor has 3 shadow register sets.

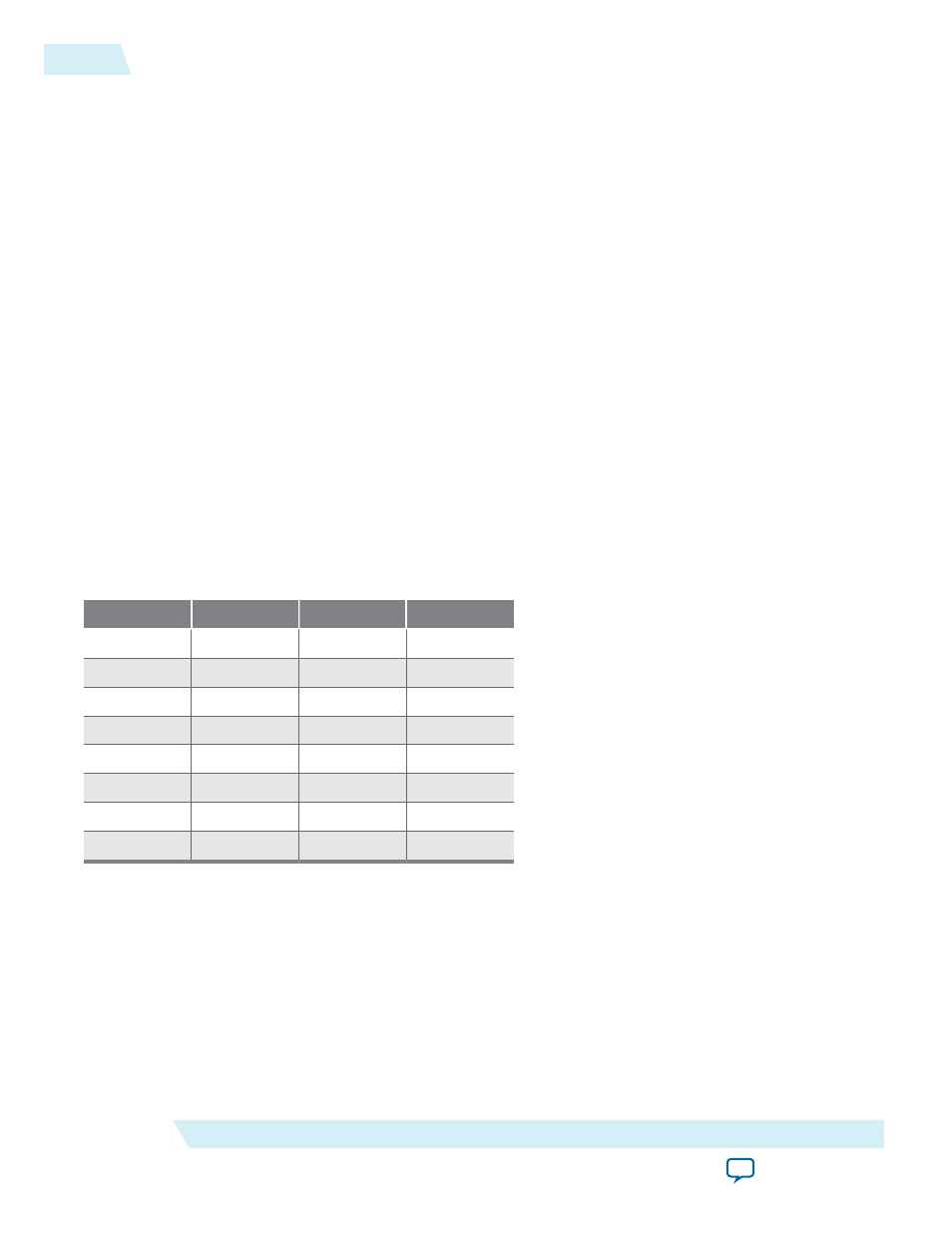

Table 28-13: Default RRS and RIL Assignment Example

VIC

IRQ

RRS

RIL

0

0

3

7

0

1

2

6

0

2

1

5

0

3

1

4

1

0

1

3

1

1

1

2

1

2

1

1

1

3

1

1

VIC BSP Design Rules for Altera Hal Implementation

The VIC BSP settings allow for a large number of combinations. This list describes some basic design

rules to follow to ensure a functional BSP:

28-22

Default Settings for RRS and RIL

UG-01085

2014.24.07

Altera Corporation

Vectored Interrupt Controller Core