Limitations, Software files, Register map – Altera Embedded Peripherals IP User Manual

Page 80: Software files -11, Register map -11

For details about the

ioctl()

Limitations

The HAL driver for the UART core does not support the endofpacket register. Refer to the Register map

section for details.

Software Files

The UART core is accompanied by the following software files. These files define the low-level interface to

the hardware, and provide the HAL drivers. Application developers should not modify these files.

•

altera_avalon_uart_regs.h

—This file defines the core's register map, providing symbolic constants to

access the low-level hardware. The symbols in this file are used only by device driver functions.

•

altera_avalon_uart.h

,

altera_avalon_uart.c

—These files implement the UART core device driver for the

HAL system library.

Register Map

Programmers using the HAL API never access the UART core directly via its registers. In general, the

register map is only useful to programmers writing a device driver for the core.

The Altera-provided HAL device driver accesses the device registers directly. If you are writing a device

driver and the HAL driver is active for the same device, your driver will conflict and fail to operate.

The UART Core Register map table below shows the register map for the UART core. Device drivers

control and communicate with the core through the memory-mapped registers.

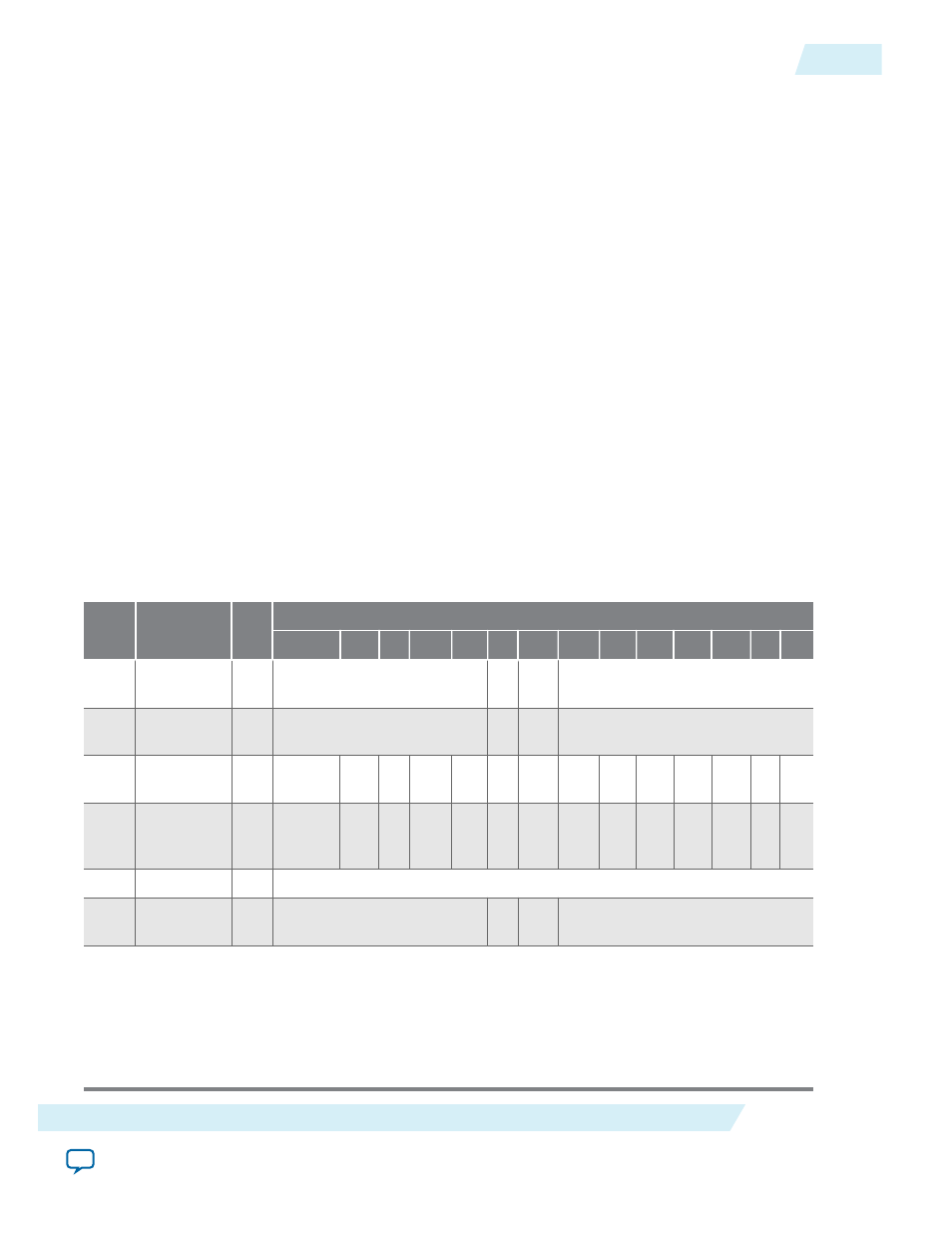

Table 8-6: UART Core Register Map

Offset

Register

Name

R/W

Description/Register Bits

15:13

12 11

10

9

8

7

6

5

4

3

2

1

0

0

rxdata

RO Reserved

Receive Data

1

txdata

WO Reserved

Transmit Data

2

status

RW Reserve

d

eop cts dcts (1) e rrdy trdy tmt toe roe brk fe p

e

3

control

RW Reserve

d

ieo

p

rts idct

s

trb

k

ie irrd

y

itrd

y

itm

t

itoe iroe ibrk ife i

p

e

4

divisor

RW Baud Rate Divisor

5

endof-

packet

RW Reserved

End-of-Packet Value

:

1. These bits may or may not exist, depending on the Data Width hardware option. If they do

not exist, they read zero, and writing has no effect.

2. Writing zero to the

status

register clears the

dcts

,

e

,

toe

,

roe

,

brk

,

fe

, and

pe

bits.

3. This register may or may not exist, depending on hardware configuration options. If it does

not exist, reading returns an undefined value and writing has no effect.

UG-01085

2014.24.07

Limitations

8-11

UART Core

Altera Corporation