Parameters, Document revision history, Parameters -3 – Altera Embedded Peripherals IP User Manual

Page 184: Document revision history -3

When the transaction is complete, the bridges send a response to the host system using the same protocol.

Parameters

For the SPI Slave to Avalon Master Bridge core, the parameter Number of synchronizer stages: Depth

allows you to specify the length of synchronization register chains. These register chains are used when a

metastable event is likely to occur and the length specified determines the meantime before failure. The

register chain length, however, affects the latency of the core.

For more information on metastability in Altera devices, refer to

For more information on metastability analysis and synchronization register chains, refer to the

Quartus II Handbook.

Document Revision History

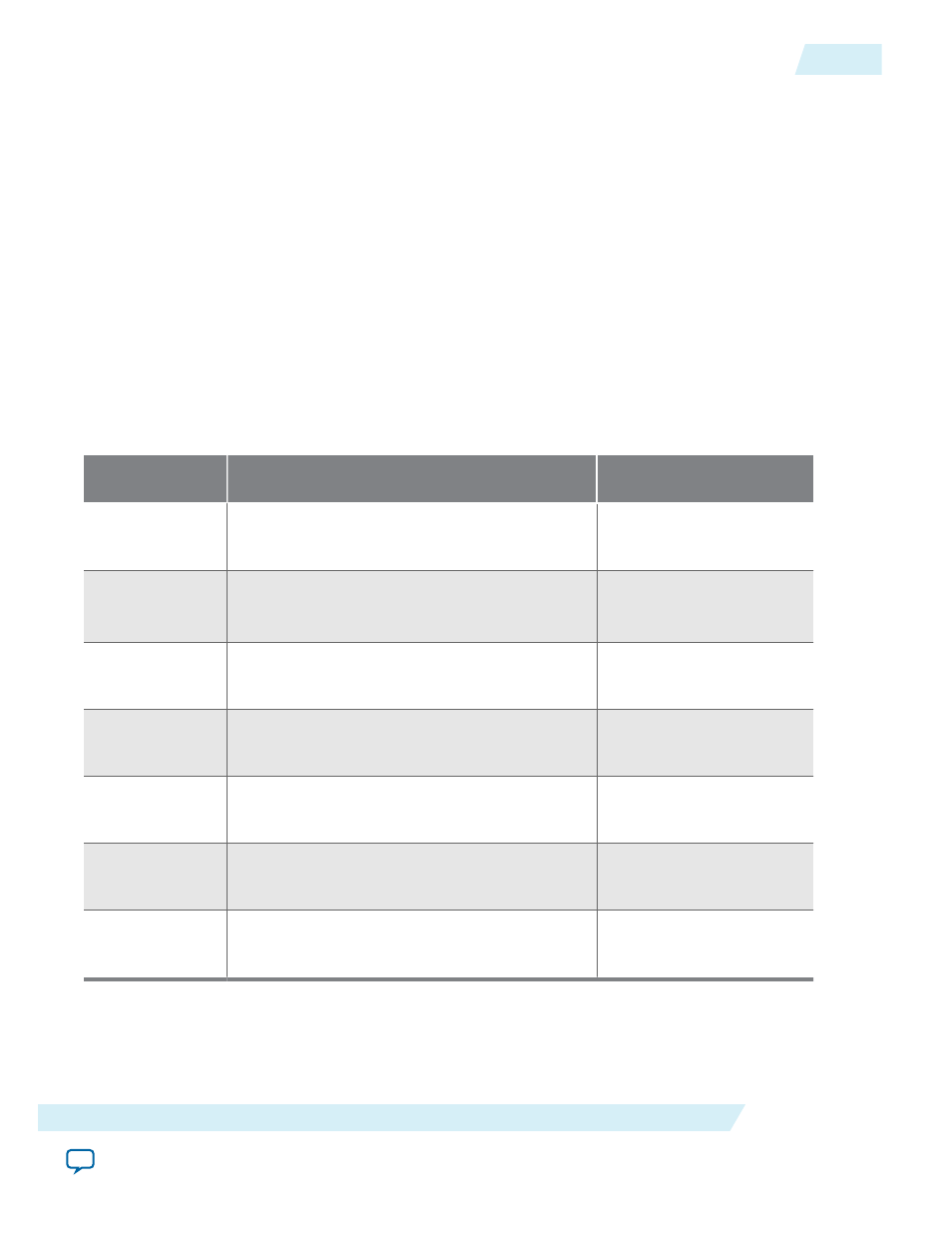

Table 18-1: Document Revision History

Date and

Document Version

Changes Made

Summary of Changes

July 2014

v14.0.0

-Removed mention of SOPC Builder, updated to

Qsys

Maintenance Release

December 2010

v10.1.0

Removed the “Device Support”, “Instantiating the

Core in SOPC Builder”, and “Referenced

Documents” sections.

—

July 2010

v10.0.0

No change from previous release.

—

November 2009

v9.1.0

No change from previous release.

—

March 2009

v9.0.0

Added description of a new parameter Number of

synchronizer stages: Depth.

—

November 2008

v8.1.0

Changed to 8-1/2 x 11 page size. No change to

content.

—

May 2008

v8.0.0

Initial release.

—

UG-01085

2014.24.07

Parameters

18-3

SPI Slave/JTAG to Avalon Master Bridge Cores

Altera Corporation