Pci-to-avalon address translation, Avalon-to-pci address translation, Pci-to-avalon address translation -6 – Altera Embedded Peripherals IP User Manual

Page 140: Avalon-to-pci address translation -6, 6 pci-to-avalon address translation, Altera corporation pci lite core send feedback

All PCI read transactions are completed as delayed reads. However, only one delayed read is accepted and

processed at a time.

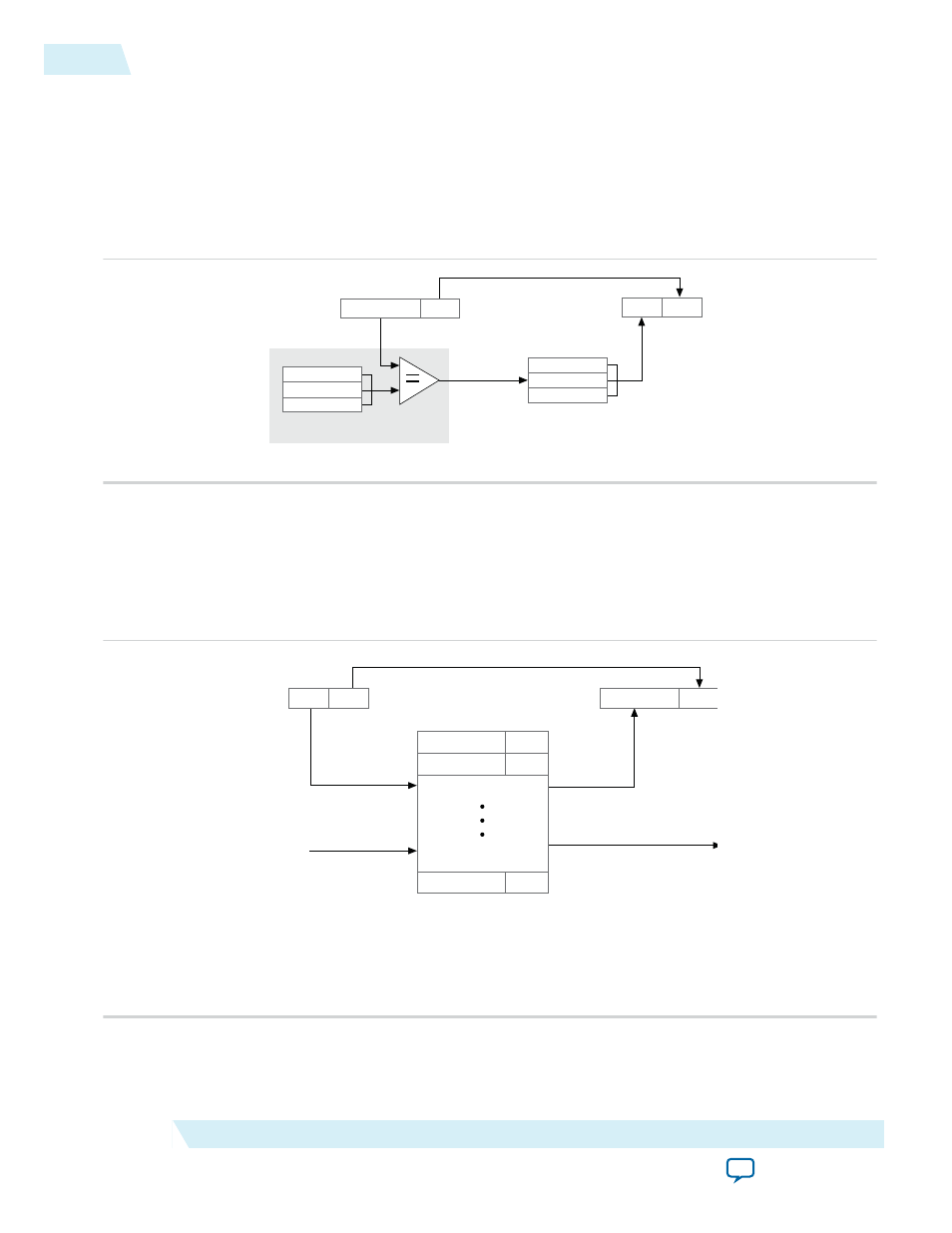

PCI-to-Avalon Address Translation

The bits in the PCI address that are used in the BAR matching process are replaced by an Avalon-MM

base address that is specific to that BAR.

Figure 14-2: PCI-to-Avalon Address Translation

Avalon_Addr_B0

Avalon Address

PCI Address

High

Low

Hardcoded BAR Specific

Avalon Addresses

Matched BAR

Selects Avalon

Addresses

Inside PCI Lite Core

BAR Specific Number

of High Avalon Bits

N = Number of Pass Thro ugh Bits (BAR Specific)

M = Number of Avalon Address Bits

P = Number of PCI Address Bits (64/32)

Low Address Bits Unchanged

(BAR Specific Number of Bits)

Avalon_Addr_B1

Avalon_Addr_B2

0

N-1

M-1

N

High

Low

0

P-1

N N-1

BAR0

BAR1

BAR2

Avalon-to-PCI Address Translation

Avalon-to-PCI address translation is done through a translation table. Low order Avalon-MM address

bits are passed to PCI unchanged; higher order Avalon-MM address bits are used to index into the

address translation table. The value found in the table entry is used as the higher order PCI address bits.

Figure 14-3: Avalon-to-PCI Address Translation

Avalon Address

PCI Address

High

Low

N = Number of Pass Thro ugh Bits

M = Number of Avalon Address Bits

P = Number of PCI Address Bits

Q = Number of Translation Ta ble Entries

Sp = Space Indication

for Each Ent

ry

Low Address Bits Unchanged

Avalon to PCI Address

Translation Ta ble

(Q Entries by P-N Bits wide)

PCI Address from

Ta

ble Entry

Used as High PCI Address Bits

Space Indication

Ta ble Updates via

Control Register

Port

High Avalon Address

Bits Index Ta ble

PCI Address

0

Sp0

PCI Address

1

Sp1

PCI Address Q-

1

SpQ-1

0

N-1

M-1

N

High

Low

0

P-1

N N-1

The address size selections in the translation table determine both the number of entries in the Avalon-to-

PCI address translation table, and the number of bits that are passed through the transaction table

unchanged.

14-6

PCI-to-Avalon Address Translation

UG-01085

2014.24.07

Altera Corporation

PCI Lite Core