Timing page – Altera Embedded Peripherals IP User Manual

Page 22

Settings

Allowed

Values

Default

Values

Description

Include a functional

memory model in the

system testbench

On, Off

On

When on, Qsys functional simulation model for the

SDRAM chip. This default memory model acceler‐

ates the process of creating and verifying systems that

use the SDRAM controller. See Hardware

Simulation Considerations section.

Based on the settings entered on the Memory Profile page, the wizard displays the expected memory

capacity of the SDRAM subsystem in units of megabytes, megabits, and number of addressable words.

Compare these expected values to the actual size of the chosen SDRAM to verify that the settings are

correct.

Timing Page

The Timing page allows designers to enter the timing specifications of the SDRAM chip(s) used. The

correct values are available in the manufacturer’s data sheet for the target SDRAM.

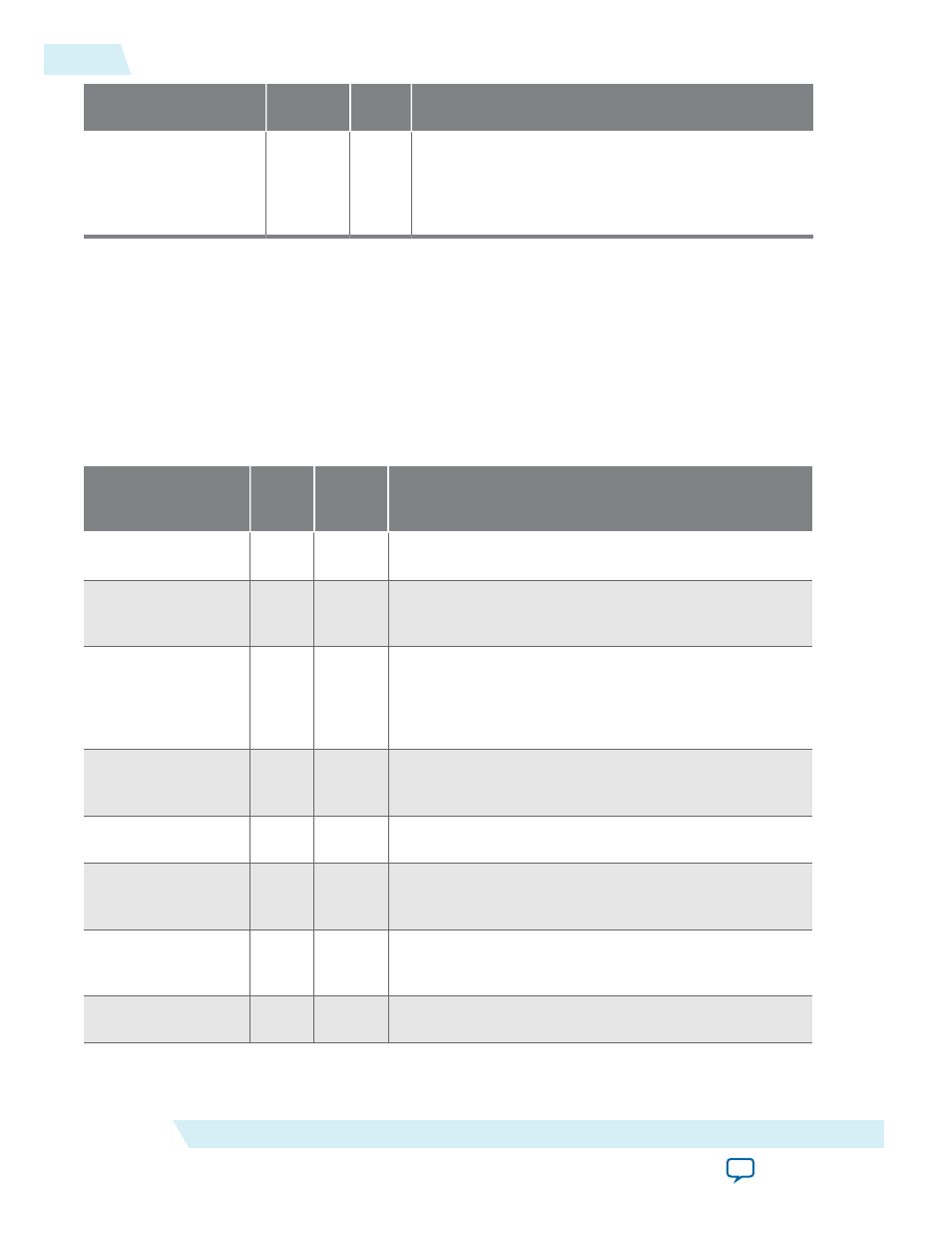

Table 2-2: Timing Page Settings

Settings

Allowe

d

Values

Default

Value

Description

CAS latency

1, 2, 3

3

Latency (in clock cycles) from a read command to data

out.

Initialization

refresh cycles

1–8

2

This value specifies how many refresh cycles the

SDRAM controller performs as part of the initialization

sequence after reset.

Issue one refresh

command every

—

15.625 µs This value specifies how often the SDRAM controller

refreshes the SDRAM. A typical SDRAM requires 4,096

refresh commands every 64 ms, which can be achieved

by issuing one refresh command every 64 ms / 4,096 =

15.625 μs.

Delay after power

up, before initiali‐

zation

—

100 µs

The delay from stable clock and power to SDRAM

initialization.

Duration of refresh

command (t_rfc)

—

70 ns

Auto Refresh period.

Duration of

precharge

command (t_rp)

—

20 ns

Precharge command period.

ACTIVE to READ

or WRITE delay

(t_rcd)

—

20 ns

ACTIVE to READ or WRITE delay.

Access time (t_ac) —

17 ns

Access time from clock edge. This value may depend on

CAS latency.

2-6

Timing Page

UG-01085

2014.24.07

Altera Corporation

SDRAM Controller Core