Functional description, Functional blocks and configurations, Functional description -3 – Altera Embedded Peripherals IP User Manual

Page 194: Functional blocks and configurations -3

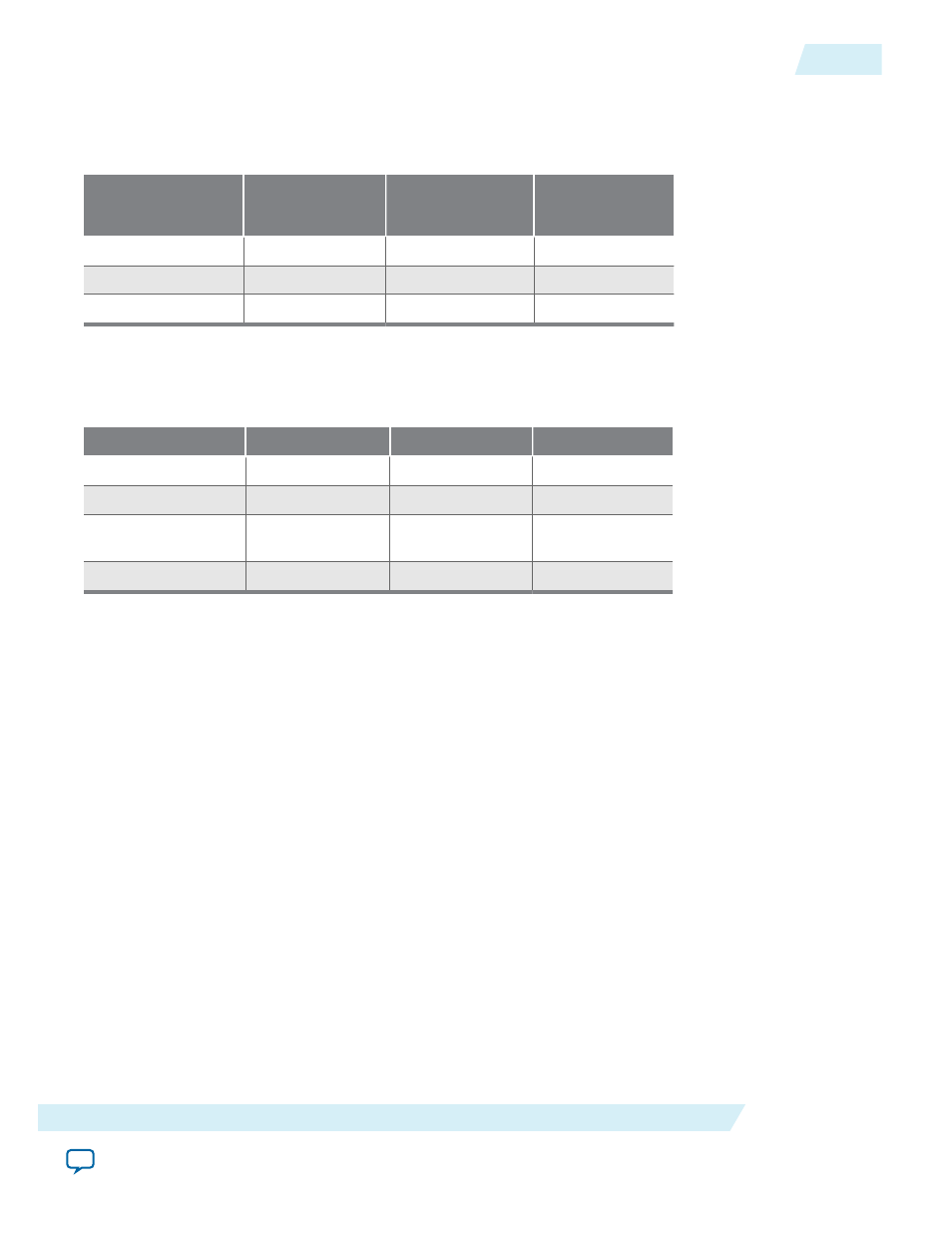

the estimated resource usage for a SG-DMA controller core used for memory to memory transfer. The

core is configurable and the resource utilization varies with the configuration specified.

Table 21-1: SG-DMA Estimated Resource Usage

Datapath

Cyclone

®

II

Stratix

®

(LEs)

Stratix II

(ALUTs)

8-bit datapath

850

650

600

32-bit datapath

1100

850

700

64-bit datapath

1250

1250

800

The core operating frequency varies with the device and the size of the datapath. The table below provides

an example of expected performance for SG-DMA cores instantiated in several different device families.

Table 21-2: SG-DMA Peak Performance

Device

Datapath

f

MAX

Throughput

Cyclone II

64 bits

150 MHz

9.6 Gbps

Cyclone III

64 bits

160 MHz

10.2 Gbps

Stratix II/Stratix II

GX

64 bits

250 MHz

16.0 Gbps

Stratix III

64 bits

300 MHz

19.2 Gbps

Functional Description

The SG-DMA controller core comprises three major blocks: descriptor processor, DMA read, and DMA

write. These blocks are combined to create three different configurations:

• Memory to memory

• Memory to stream

• Stream to memory

The type of devices you are transferring data to and from determines the configuration to implement.

Examples of memory-mapped devices are PCI, PCIe and most memory devices. The Triple Speed

Ethernet MAC, DSP MegaCore functions and many video IPs are examples of streaming devices. A

recompilation is necessary each time you change the configuration of the SG-DMA controller core.

Functional Blocks and Configurations

The following sections describe each functional block and configuration.

UG-01085

2014.24.07

Functional Description

21-3

Scatter-Gather DMA Controller Core

Altera Corporation