Altera Embedded Peripherals IP User Manual

Page 276

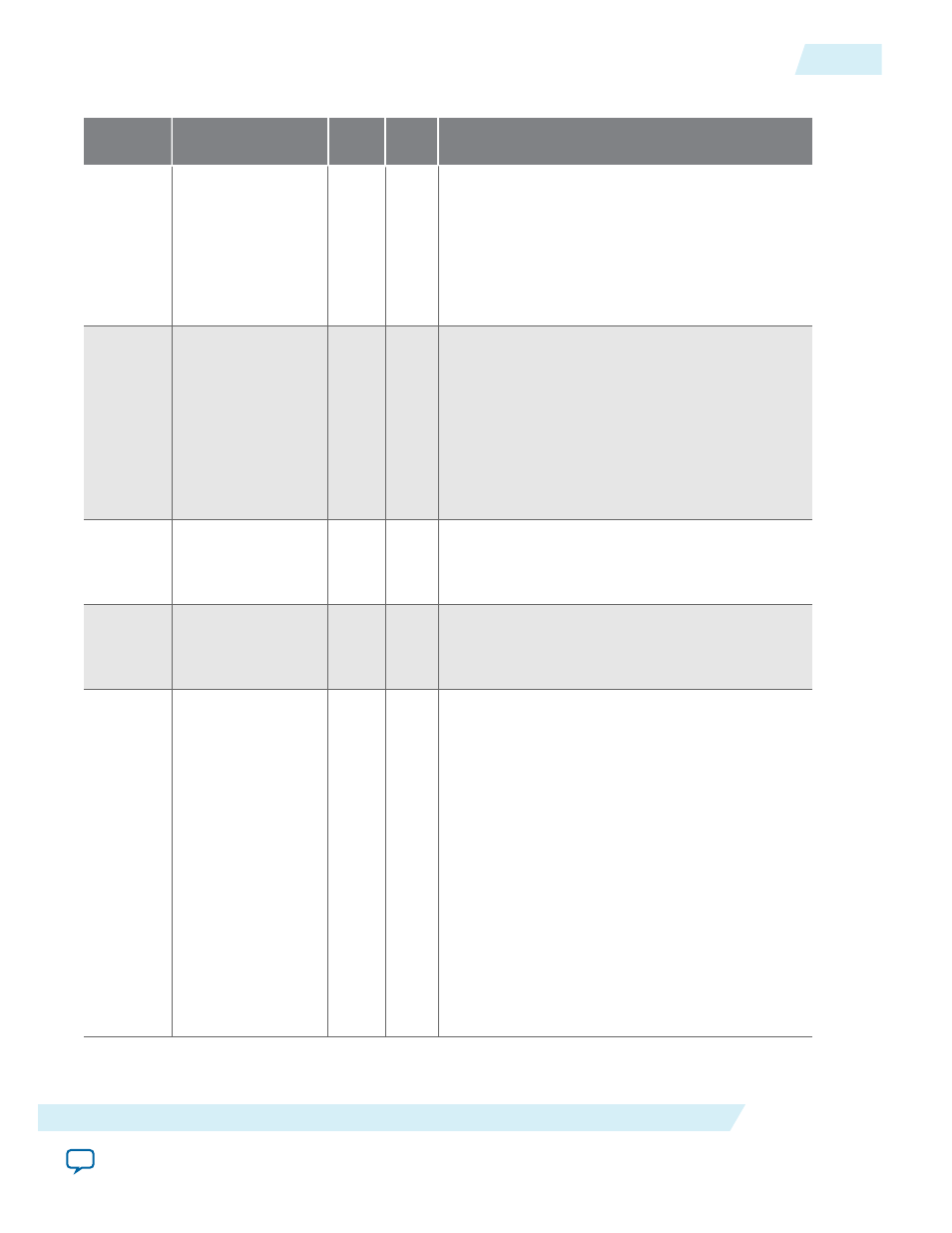

Table 28-6: Control Status Registers

Offset

Register Name

Access Reset

Value

Description

0 – 31

INT_CONFIG

<n>

R/W

0

There are 32 interrupt configuration registers

(

INT_CONFIG0

–

INT_CONFIG31

). Each register

contains fields to configure the behavior of its

corresponding interrupt. If an interrupt input

does not exist, reading the corresponding register

always returns zero, and writing is ignored. Refer

to the INT_CONFIG Register Map table for the

INT_CONFIG

register map.

32

INT_ENABLE

R/W

0

The interrupt enable register.

INT_ENABLE

holds

the enabled status of each interrupt input. The 32

bits of the register map to the 32 interrupts

available in the VIC core. For example, bit 5

Interrupt that are not enabled are never

considered by the priority processing block, even

when the interrupt input is asserted. This applies

to both maskable and non-maskable interrupts.

33

INT_ENABLE_SET

W

0

The interrupt enable set register. Writing a 1 to a

bit in

INT_ENABLE_SET

sets the corresponding bit

in

INT_ENABLE

. Writing a 0 to a bit has no effect.

Reading from this register always returns 0.

34

INT_ENABLE_CLR

W

0

The interrupt enable clear register. Writing a 1 to

a bit in

INT_ENABLE_CLR

clears corresponding bit

in

INT_ENABLE

. Writing a 0 to a bit has no effect.

Reading from this register always returns 0.

35

INT_PENDING

R

0

The interrupt pending register.

INT_PENDING

shows the pending interrupts. Each bit

corresponds to one interrupt input.

If an interrupt does not exist, reading its

corresponding

INT_PENDING

bit always returns 0,

and writing is ignored.

Bits in

INT_PENDING

are set in the following ways:

An external interrupt is asserted at the VIC

interface and the corresponding

INT_ENABLE

bit

is set.

An

SW_INTERRUPT

bit is set and the

corresponding

INT_ENABLE

bit is set.

INT_PENDING

bits remain set as long as either

condition applies. Refer to the Interrupt Request

Block for details.

UG-01085

2014.24.07

Register Maps

28-7

Vectored Interrupt Controller Core

Altera Corporation