Altera Embedded Peripherals IP User Manual

Page 315

For each advanced signal present on the ALTPLL megafunction, you can select one of the following access

modes:

• Export—Exports the signal to the top level of the SOPC builder system module.

• Register—Maps the signal to a bit in a status or control register.

The advanced signals are optional. If you choose not to create any of them in the ALTPLL

MegaWizard Plug-In, the PLL's default behavior is as shown in below.

You can specify the access mode for the advanced signals shown in below. The ALTPLL core signals,

not displayed in this table, are automatically exported to the top level of the SOPC Builder system

module.

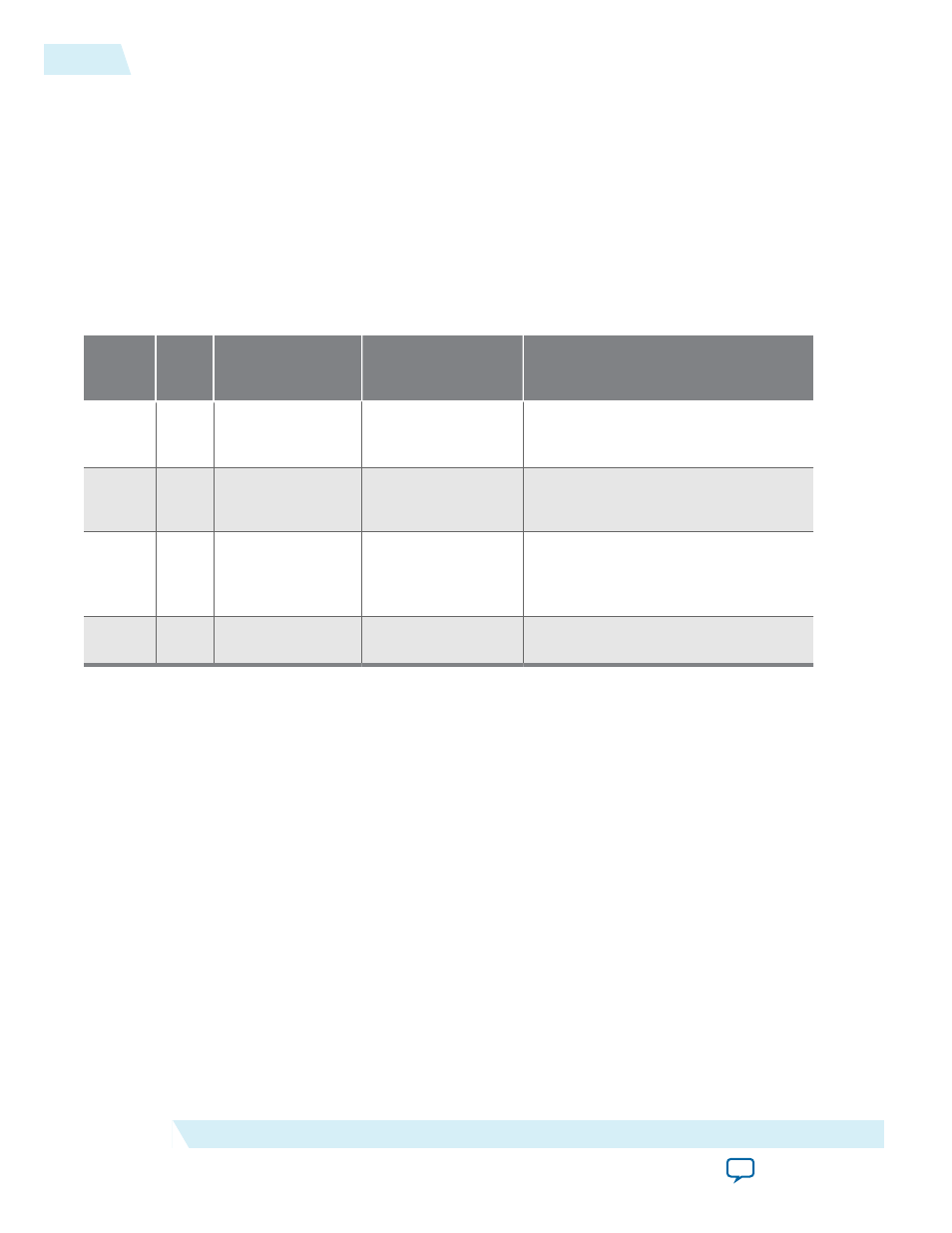

Table 32-1: ALTPLL Advanced Signal

ALTPLL

Name

Input /

Outpu

t

Avalon-MM PLL

Wizard Name

Default Behavior

Description

ares

et

input PLL Reset Input

The PLL is reset only

at device configura‐

tion.

This signal resets the entire SOPC

Builder system module, and restores

the PLL to its initial settings.

plle

na

input PLL Enable Input

The PLL is enabled.

This signal enables the PLL.

pllena

is always exported.

pfde

na

input PFD Enable Input

The phase-frequency

detector is enabled.

This signal enables the phase-

frequency detector in the PLL,

allowing it to lock on to changes in

the clock reference.

lock

ed

output PLL Locked Output —

This signal is asserted when the PLL

is locked to the input clock.

Asserting

areset

resets the entire SOPC Builder system module, not just the PLL.

Finish

Click Finish to insert the PLL into the SOPC Builder system. The PLL clock output(s) appear in the clock

settings table on the SOPC Builder System Contents tab.

If the PLL has external output clocks, they appear in the clock settings table like other clocks; however,

you cannot use them to drive components within the SOPC Builder system.

For details about using external output clocks, refer to the

The SOPC Builder automatically connects the PLL's reference clock input to the first available clock in the

clock settings table.

If there is more than one SOPC Builder system clock available, verify that the PLL is connected to the

appropriate reference clock.

32-4

Instantiating the PLL Core

UG-01085

2014.24.07

Altera Corporation

PLL Cores