Simulation considerations, Software programming model, Hal system library support – Altera Embedded Peripherals IP User Manual

Page 201: Software files, Register maps, Simulation considerations -10, Software programming model -10, Hal system library support -10, Software files -10, Register maps -10

Simulation Considerations

Signals for hardware simulation are automatically generated as part of the Nios II simulation process

available in the Nios II IDE.

Software Programming Model

The following sections describe the software programming model for the SG-DMA controller core.

HAL System Library Support

The Altera-provided driver implements a HAL device driver that integrates into the HAL system library

for Nios II systems. HAL users should access the SG-DMA controller core via the familiar HAL API and

the ANSI C standard library.

Software Files

The SG-DMA controller core provides the following software files. These files provide low-level access to

the hardware and drivers that integrate into the Nios II HAL system library. Application developers

should not modify these files.

•

altera_avalon_sgdma_regs.h

—defines the core's register map, providing symbolic constants to access the

low-level hardware

•

altera_avalon_sgdma.h

—provides definitions for the Altera Avalon SG-DMA buffer control and status

flags.

•

altera_avalon_sgdma.c

—provides function definitions for the code that implements the SG-DMA

controller core.

•

altera_avalon_sgdma_descriptor.h

—defines the core's descriptor, providing symbolic constants to access

the low-level hardware.

Register Maps

The SG-DMA controller core has three registers accessible from its Avalon-MM interface;

status

,

control

and

next_descriptor_pointer

. Software can configure the core and determines its current

status by accessing the registers.

The

control

/

status

register has a 32-bit interface without byte-enable logic, and therefore cannot be

properly accessed by a master with narrower data width than itself. To ensure correct operation of the

core, always access the register with a master that is at least 32 bits wide.

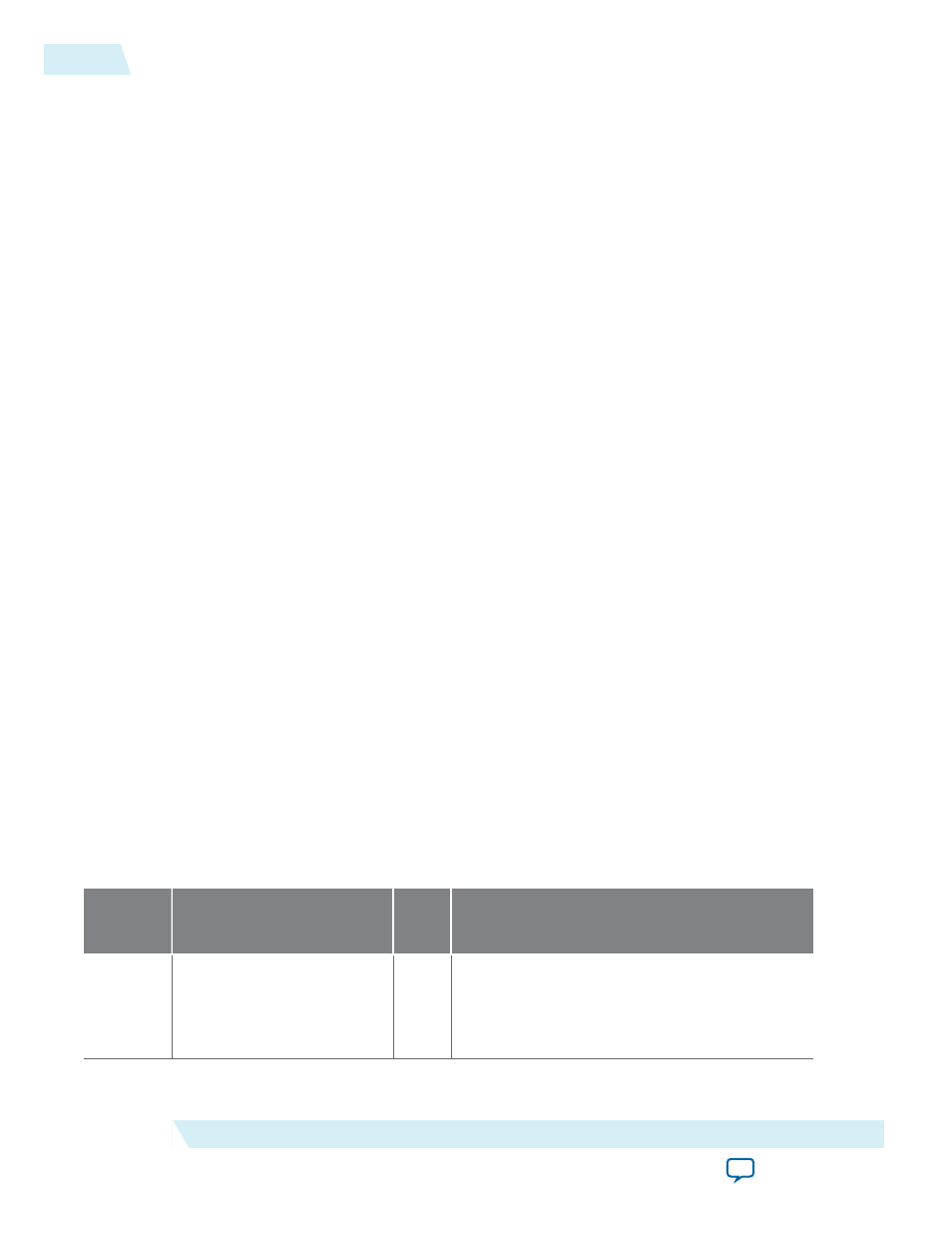

Table 21-6: Register Map

32-bit

Word

Offset

Register Name

Reset

Value

Description

base +

0

status

0

This register indicates the core’s current status

such as what caused the last interrupt and if the

core is still processing descriptors. See the

status Register Map table for the

status

register map.

21-10

Simulation Considerations

UG-01085

2014.24.07

Altera Corporation

Scatter-Gather DMA Controller Core