Dma support, Fpga resource usage, Dma support -5 – Altera Embedded Peripherals IP User Manual

Page 91: Fpga resource usage -5

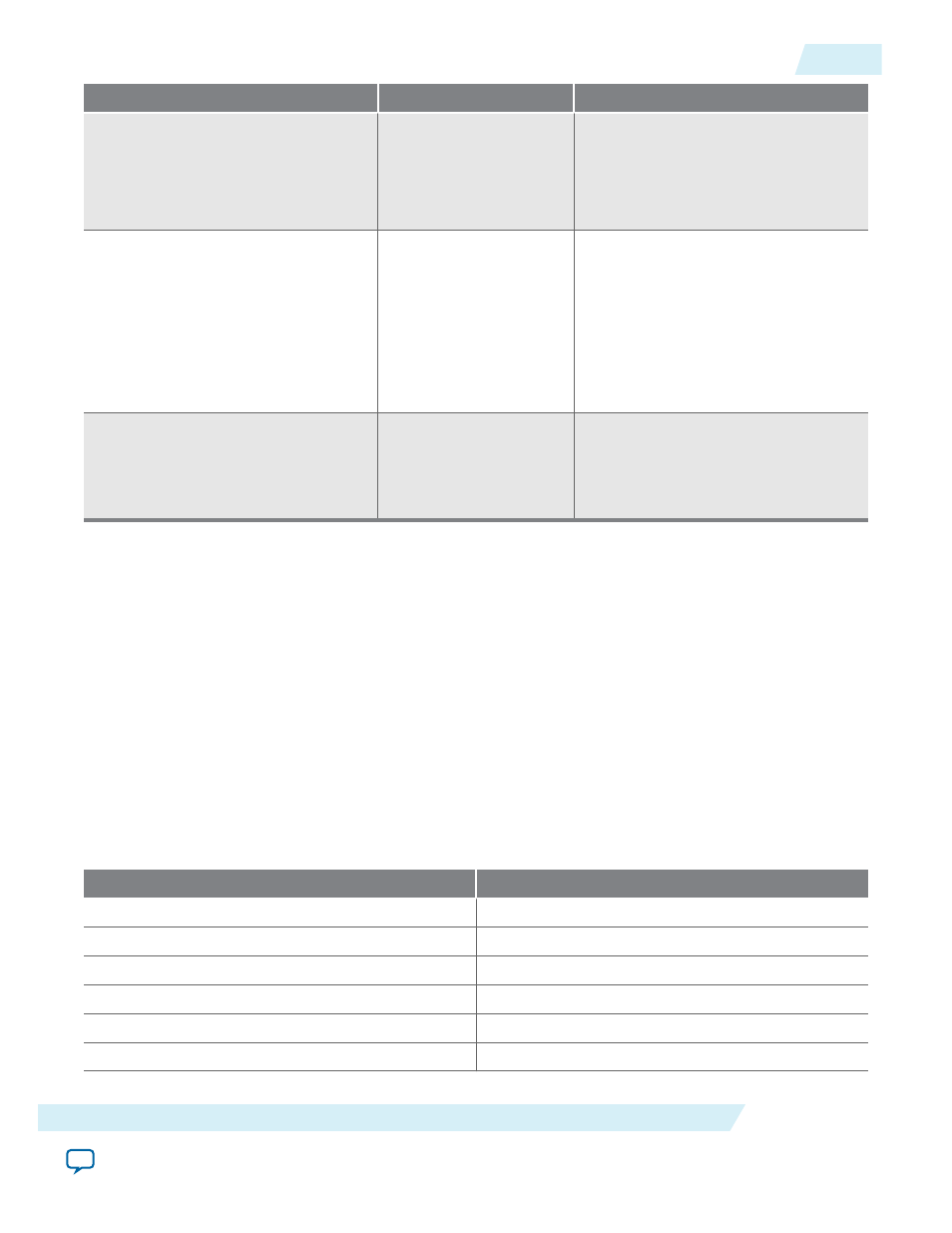

Parameter Name

Description

Default

FIFO_DEPTH

Set depth of FIFO

Values limited to 32, 64

and 128

FIFO_MODE

must be 1.

128

FIFO_HWFC

1 = Enabled Hardware

Flow Control

0 = Disabled Hardware

Flow Control

Mutually exclusive with

FIFO_SWFC

FIFO_MODE

must be 1

1

DMA_EXTRA

1 = Additional DMA

Interface Enabled

0 = Additional DMA

Interface Disabled

1

DMA Support

DMA support is only available when used with the HPS DMA controller. The HPS DMA controller has

the required handshake signals to control DMA data transfers with the IP. This is the same method used

by all IPs within the HPS itself.

For more information about the HPS DMA Controller handshake signals, refer to the DMA Controller

chapter in the Cyclone V Device Handbook, Volume 3.

FPGA Resource Usage

In order to optimize resource usage, in terms of register counts, the UART IP design specifically targets

MLABs to be used as FIFO storage element. Below are the FPGA resources required for one UART with

128 Byte Tx and Rx FIFO.

Table 9-9: UART Resource Usage

Resource

Number

ALMS needed

362

Total LABs

54

Combinational ALUT usage for logic

436

Combinational ALUT usage for route-throughs

17

Dedicated logic registers

311

Design implementation registers

294

UG-01085

2014.24.07

DMA Support

9-5

16550 UART

Altera Corporation