Altera Embedded Peripherals IP User Manual

Page 164

base + 5

almostempty

The table below outlines the use of the various fields of the

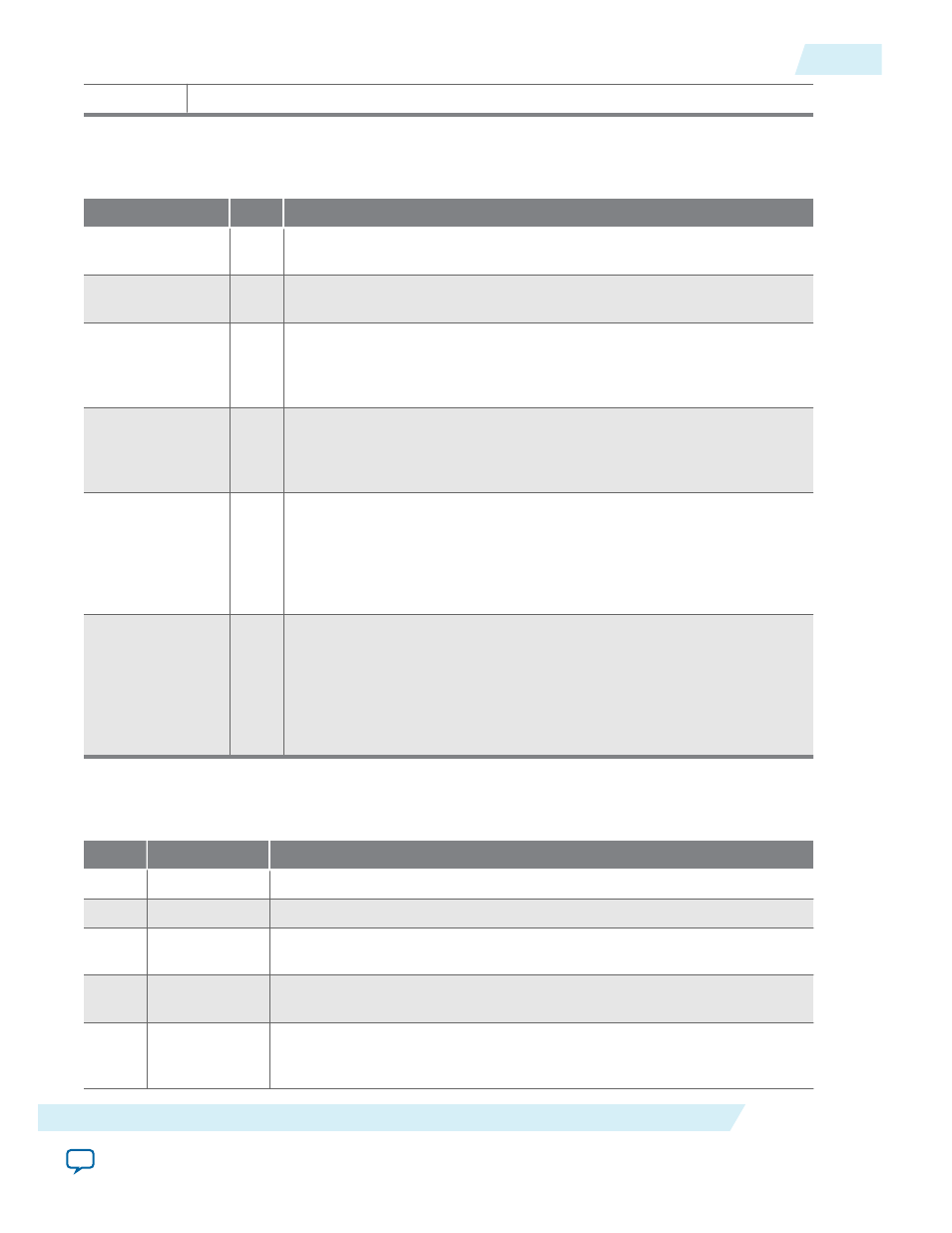

Table 16-4: FIFO Status Field Descriptions

Field

Type

Description

fill_level

RO

The instantaneous fill level of the FIFO, provided in units of symbols for

a FIFO with an Avalon-ST FIFO and words for an Avalon-MM FIFO.

i_status

RO

A 6-bit register that shows the FIFO’s instantaneous status. See Status

Bit Field Description Table for the meaning of each bit field.

event

RW1

C

A 6-bit register with exactly the same fields as i_

status

. When a bit in

the i_

status

register is set, the same bit in the

event

register is set. The

bit in the

event

register is only cleared when software writes a 1 to that

bit.

interrupten-

able

RW

A 6-bit interrupt enable register with exactly the same fields as the

event

and i_

status

registers. When a bit in the

event

register

transitions from a 0 to a 1, and the corresponding bit in

interrupten-

able

is set, the master Is interrupted.

almostfull

RW

A threshold level used for interrupts and status. Can be written by the

Avalon-MM status master at any time. The default threshold value for

DCFIFO is Depth-4. The default threshold value for SCFIFO is Depth-1.

The valid range of the threshold value is from 1 to the default. 1 is used

when attempting to write a value smaller than 1. The default is used

when attempting to write a value larger than the default.

almostempty

RW

A threshold level used for interrupts and status. Can be written by the

Avalon-MM status master at any time. The default threshold value for

DCFIFO is 1. The default threshold value for SCFIFO is 1. The valid

range of the threshold value is from 1 to the maximum allowable

almostfull

threshold. 1 is used when attempting to write a value

smaller than 1. The maximum allowable is used when attempting to

write a value larger than the maximum allowable.

status

register.

Table 16-5: Status Bit Field Descriptions

Bit(s)

Name

Description

0

FULL

Has a value of 1 if the FIFO is currently full.

1

EMPTY

Has a value of 1 if the FIFO is currently empty.

2

ALMOSTFULL

Has a value of 1 if the fill level of the FIFO is greater than the

almostfull

value.

3

ALMOSTEMPTY

Has a value of 1 if the fill level of the FIFO is less than the

almostempty

value.

4

OVERFLOW

Is set to 1 for 1 cycle every time the FIFO overflows. The FIFO overflows

when an Avalon write master writes to a full FIFO. OVERFLOW is only

valid when Allow backpressure is off.

UG-01085

2014.24.07

Software Control

16-9

On-Chip FIFO Memory Core

Altera Corporation