Master and target performance, Master performance, Target performance – Altera Embedded Peripherals IP User Manual

Page 139: Master and target performance -5

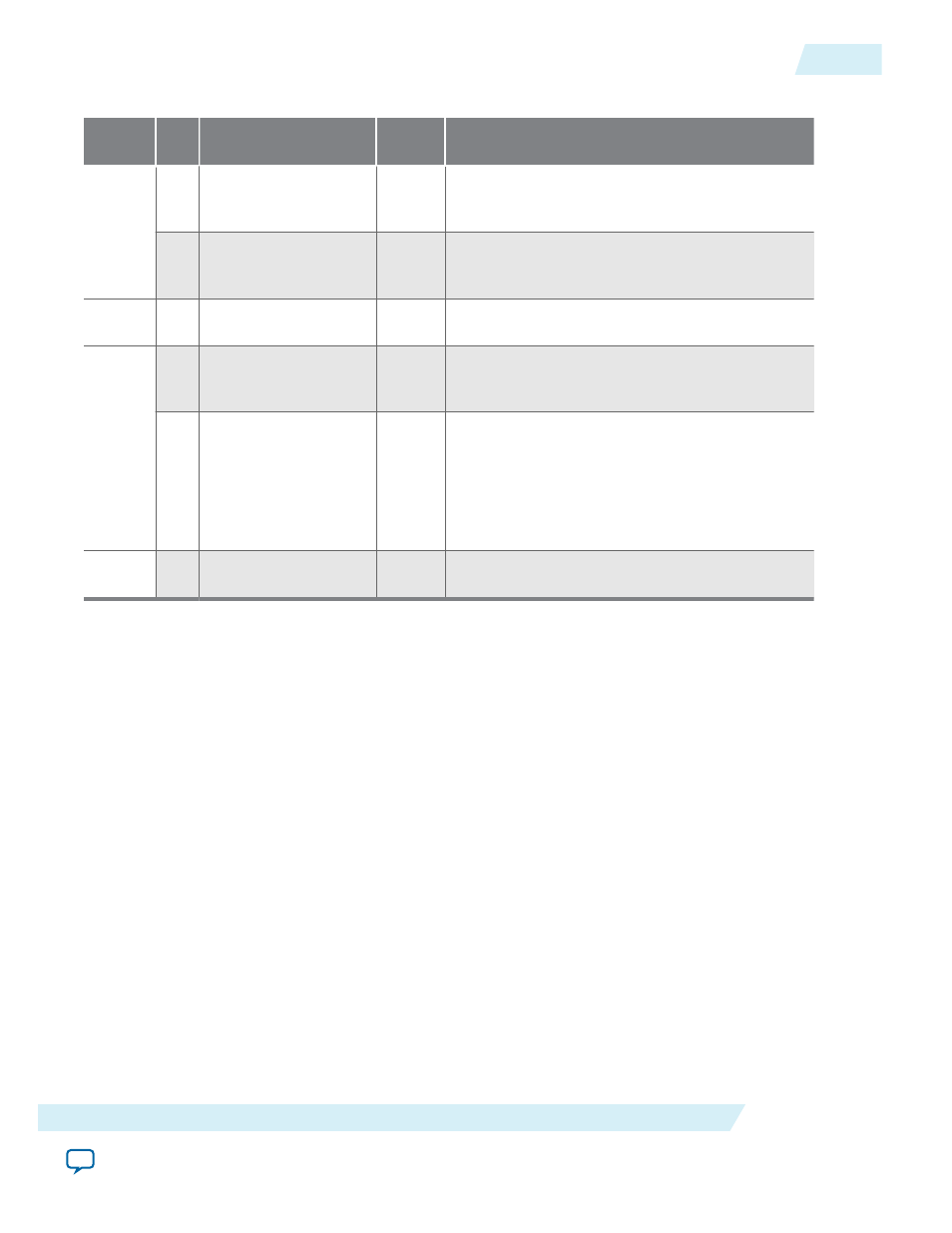

Table 14-3: Avalon-to-PCI Address Translation Table – Address Range: 0x1000-0x1FFF

Address

Bit

Name

Access

Mode

Description

0x10

00

1:0

A2P_ADDR_SPACE0

W

Address space indication for entry 0. See

Address Space Bit Encodings table for the

definition of these bits.

31:2

A2P_ADDR_MAP_LO0

W

Lower bits of Avalon-to-PCI address map entry

0. The pass through bits are not writable and are

forced to 0.

0x10

04

31:0

A2P_ADDR_MAP_HI0

W

Reserved.

0x10

08

1:0

A2P_ADDR_SPACE1

W

Address Space indication for entry 1. See

Address Space bit Encodings for the definition

of these bits.

31:2

A2P_ADDR_MAP_LO1

W

Lower bits of Avalon-to-PCI address map entry

1. Pass through bits are not writable and are

forced to 0.

This entry is only implemented if the number of

pages in the address translation table is greater

than 1.

0x10

0C

31:0

A2P_ADDR_MAP_HI1

W

Reserved.

Master and Target Performance

The performance of the PCI Lite core is designed to provide low-latency single-cycle and burst

transactions.

Master Performance

The master provides high throughput for transactions initiated by Avalon-MM master devices to PCI

target devices via the PCI bus master interface. Avalon-MM read transactions are implemented as latent

read transfers. The PCI master device issues only one read transaction at a time.

The PCI bus access (PBA) handles the Avalon master transaction system interconnect hold state for 6

clock cycles. This is the maximum number of cycles supported by the PCI specification.

Target Performance

The target allows high throughput read/write operations to Avalon-MM slave peripherals. Read/write

accesses to prefetchable base address registers (BARs) use dual-port buffers to enable burst transactions

on both the PCI and Avalon-MM sides. This profile also allows access to the PCI BARs (Prefetchable,

Non-Prefetchable, and I/O) to use their respective Avalon-MM master ports to initiate transfers to

Avalon-MM slave peripherals. Prefetchable handles burst transaction and Non-Prefetchable and I/O

handles only single-cycle transaction.

UG-01085

2014.24.07

Master and Target Performance

14-5

PCI Lite Core

Altera Corporation