Interrupt after each descriptor is processed – Altera Embedded Peripherals IP User Manual

Page 203

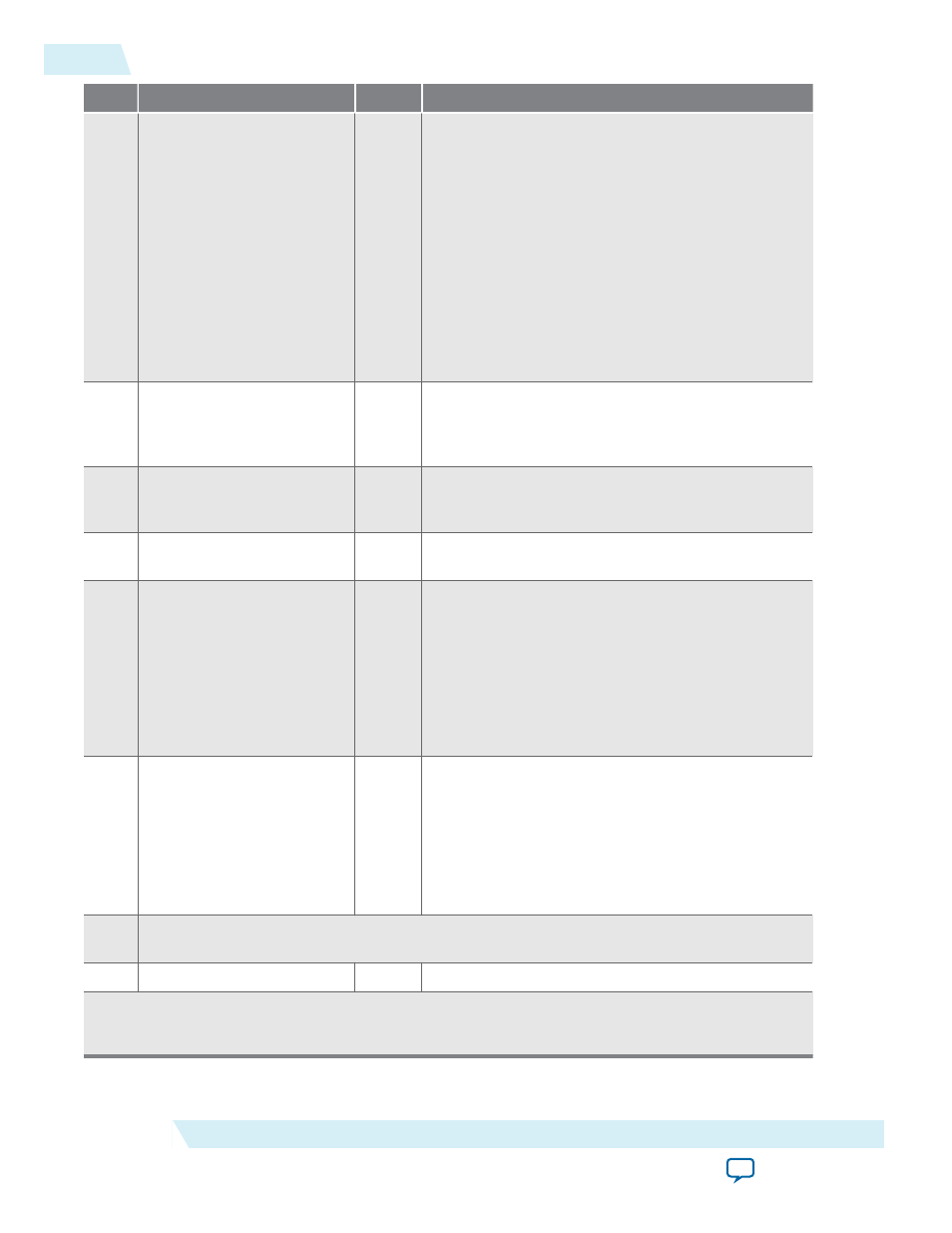

Bit

Bit Name

Access

Description

5

RUN

R/W

Set this bit to 1 to start the descriptor processor

block which subsequently initiates DMA transac‐

tions. Prior to setting this bit to 1, ensure that the

register

next_descriptor_pointer

is updated with

the address of the first descriptor to process. The

core continues to process descriptors in its queue as

long as this bit is 1.

Clear this bit to stop the core from processing the

next descriptor in its queue. If this bit is cleared in

the middle of processing a descriptor, the core

completes the processing before stopping. The host

processor can then modify the remaining descrip‐

tors and restart the core.

6

STOP_DMA_ER

R/W

Set this bit to 1 to stop the core when an Avalon-ST

error is encountered during a DMA transaction.

This bit applies only to stream-to-memory configu‐

rations.

7

IE_MAX_DESC_PROCESSED

R/W

Set this bit to 1 to generate an interrupt after the

number of descriptors specified by

MAX_DESC_

PROCESSED

are processed.

8 ..

15

MAX_DESC_PROCESSED

R/W

Specifies the number of descriptors to process

before the core generates an interrupt.

16

SW_RESET

R/W

Software can reset the core by writing to this bit

twice. Upon the second write, the core is reset. The

logic which sequences the software reset process

then resets itself automatically.

Executing a software reset when a DMA transfer is

active may result in permanent bus lockup until the

next system reset. Hence, Altera recommends that

you use the software reset as your last resort.

17

PARK

R/W

Seting this bit to 0 causes the SG-DMA controller

core to clear the

OWNED_BY_HW

bit in the descriptor

after each descriptor is processed. If the

PARK

bit is

set to 1, the core does not clear the

OWNED_BY_HW

bit, thus allowing the same descriptor to be

processed repeatedly without software intervention.

You also need to set the last descriptor in the list to

point to the first one.

18.

.30

Reserved

31

CLEAR_INTERRUPT

R/W

Set this bit to 1 to clear pending interrupts.

1. All interrupts are generated only after the descriptor is updated.

21-12

Register Maps

UG-01085

2014.24.07

Altera Corporation

Scatter-Gather DMA Controller Core