Altera Embedded Peripherals IP User Manual

Page 178

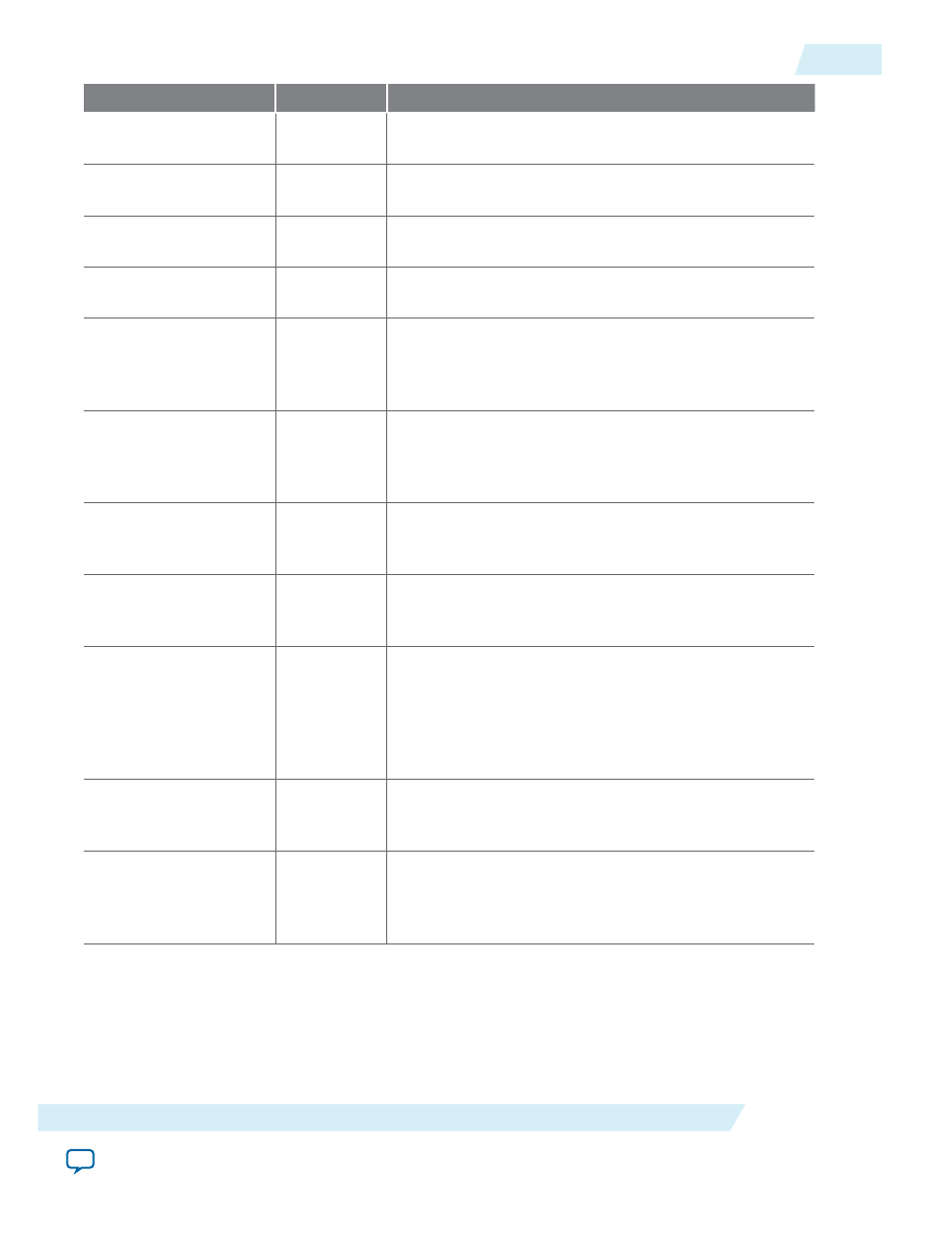

Parameter

Legal Values

Description

Error width

0–32

The width of the

error

signal on the Avalon-ST data

interfaces.

FIFO depth

2–2

32

The depth of each memory segment allocated for a

channel. The value must be a multiple of 2.

Use packets

0 or 1

Setting this parameter to 1 enables packet support on the

Avalon-ST data interfaces.

Use fill level

0 or 1

Setting this parameter to 1 enables the Avalon-MM

status interface.

Number of almost-full

thresholds

0 to 2

The number of almost-full thresholds to enable. Setting

this parameter to 1 enables Use almost-full threshold 1.

Setting it to 2 enables both Use almost-full threshold 1

and Use almost-full threshold 2.

Number of almost-

empty thresholds

0 to 2

The number of almost-empty thresholds to enable.

Setting this parameter to 1 enables Use almost-empty

threshold 1. Setting it to 2 enables both Use almost-

empty threshold 1 and Use almost-empty threshold 2.

Section available

threshold

0 to 2

Address

Width

Specify the amount of data to be delivered to the output

interface. This parameter applies only when packet

support is disabled.

Packet buffer mode

0 or 1

Setting this parameter to 1 causes the core to deliver only

full packets to the output interface. This parameter

applies only when Use packets is set to 1.

Drop on error

0 or 1

Setting this parameter to 1 causes the core to drop

packets at the Avalon-ST data sink interface if the

error

signal on that interface is asserted. Otherwise, the core

accepts the packet and sends it out on the Avalon-ST

data source interface with the same error. This parameter

applies only when packet buffer mode is enabled.

Address width

1–32

The width of the FIFO address. This parameter is

determined by the parameter FIFO depth; FIFO depth =

2

Address Width

.

Use request

—

Turn on this parameter to implement the Avalon-MM

request interface. If the core is configured to support

more than one channel and the request interface is

disabled, only channel 0 is accessible.

UG-01085

2014.24.07

Parameters

17-5

Avalon-ST Multi-Channel Shared Memory FIFO Core

Altera Corporation