Document revision history, Document revision history -11 – Altera Embedded Peripherals IP User Manual

Page 68

The JTAG UART core has two kinds of interrupts: write interrupts and read interrupts. The WE and RE

bits in the

control

register enable/disable the interrupts.

The core can assert a write interrupt whenever the write FIFO is nearly empty. The nearly empty

threshold,

write_threshold

, is specified at system generation time and cannot be changed by embedded

software. The write interrupt condition is set whenever there are

write_threshold

or fewer characters in

the write FIFO. It is cleared by writing characters to fill the write FIFO beyond the

write_threshold

.

Embedded software should only enable write interrupts after filling the write FIFO. If it has no characters

remaining to send, embedded software should disable the write interrupt.

The core can assert a read interrupt whenever the read FIFO is nearly full. The nearly full threshold value,

read_threshold

, is specified at system generation time and cannot be changed by embedded software.

The read interrupt condition is set whenever the read FIFO has

read_threshold

or fewer spaces

remaining. The read interrupt condition is also set if there is at least one character in the read FIFO and

no more characters are expected. The read interrupt is cleared by reading characters from the read FIFO.

For optimum performance, the interrupt thresholds should match the interrupt response time of the

embedded software. For example, with a 10-MHz JTAG clock, a new character is provided (or consumed)

by the host PC every 1 µs. With a threshold of 8, the interrupt response time must be less than 8 µs. If the

interrupt response time is too long, performance suffers. If it is too short, interrupts occurs too often.

For Nios II processor systems, read and write thresholds of 8 are an appropriate default.

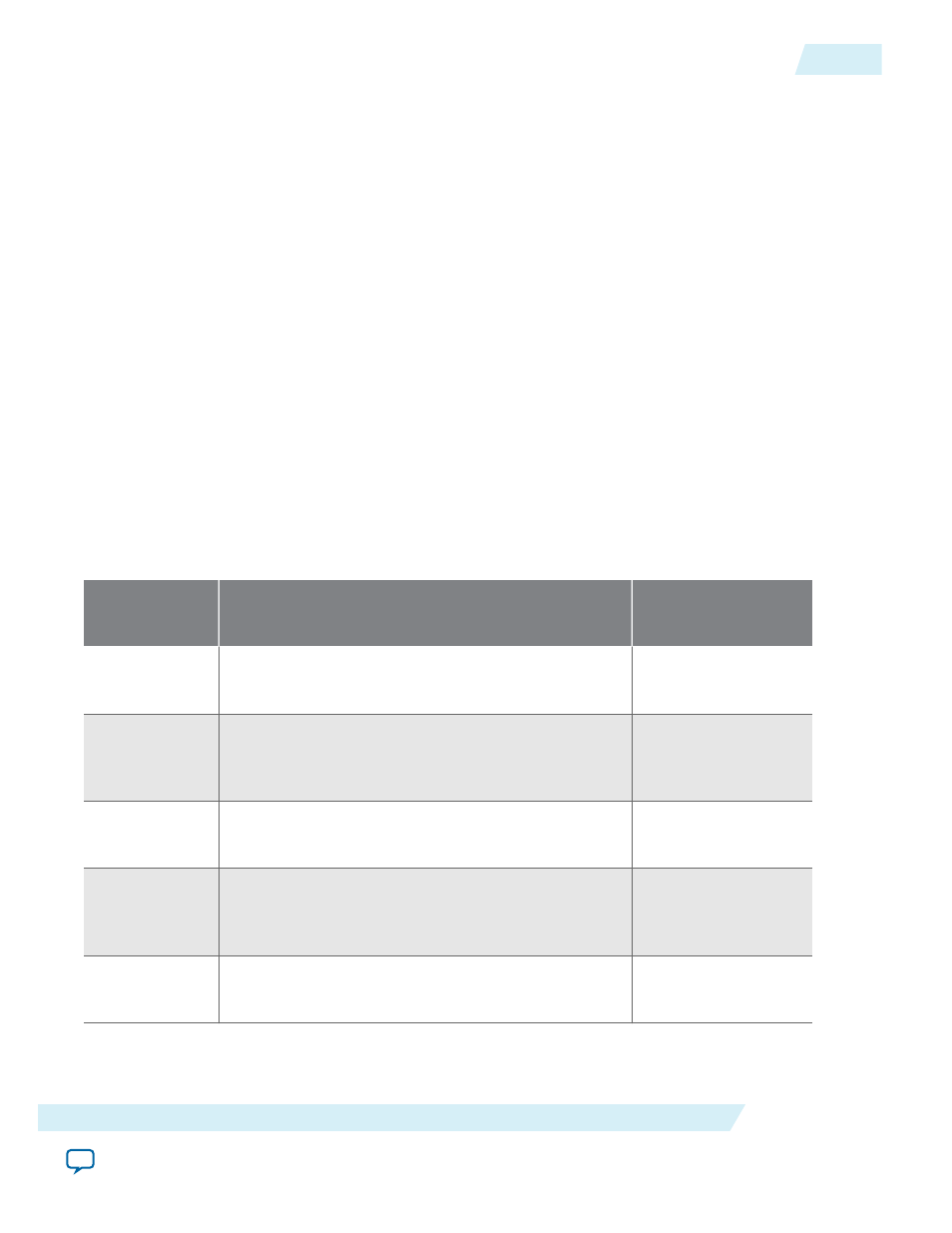

Document Revision History

Table 7-7: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

July 2014

V14.0.0

-Removed metion of SOPC Builder, updated to Qsys

Maintance Release

December

2010

v10.1.0

Removed the “Device Support”, “Instantiating the Core in

SOPC Builder”, and “Referenced Documents” sections.

—

July 2010

v10.0.0

No change from previous release.

—

November

2009

v9.1.0

No change from previous release.

—

March 2009

v9.0.0

No change from previous release.

—

UG-01085

2014.24.07

Document Revision History

7-11

JTAG UART Core

Altera Corporation