Figure, Displays the bit ass – Zilog Z80230 User Manual

Page 150

SCC/ESCC

User Manual

UM010903-0515

Register Descriptions

143

This bit enables the Wait/Request function in conjunction with the Request/Wait Function Select

bit (D6).

Write Register 1

When programmed to 0, the selected function (bit 6) forces the /W//REQ pin into the appropriate

inactive state (High for Request, floating for Wait).

When programmed to 1, the state of bit 6 determines the activity of the /W//REQ pin (Wait or

Request).

Bit 6: WAIT/DMA Request Function

When programmed to 0, the Wait function is selected. In the Wait mode, the /W//REQ pin

switches from floating to Low when the CPU attempts to transfer data before the SCC is ready.

When programmed to 1, the Request function is selected. In the Request mode, the /W//REQ pin

switches from High to Low when the SCC is ready to transfer data.

Bit 5: /WAIT//REQUEST on Transmit or Receive

When programmed to 0, the state of the /W//REQ pin is determined by bit 6 and the state of the

transmit buffer.

A transmit request function is available on the /DTR//REQ pin. This allows full-duplex

operation under DMA control for both channels.

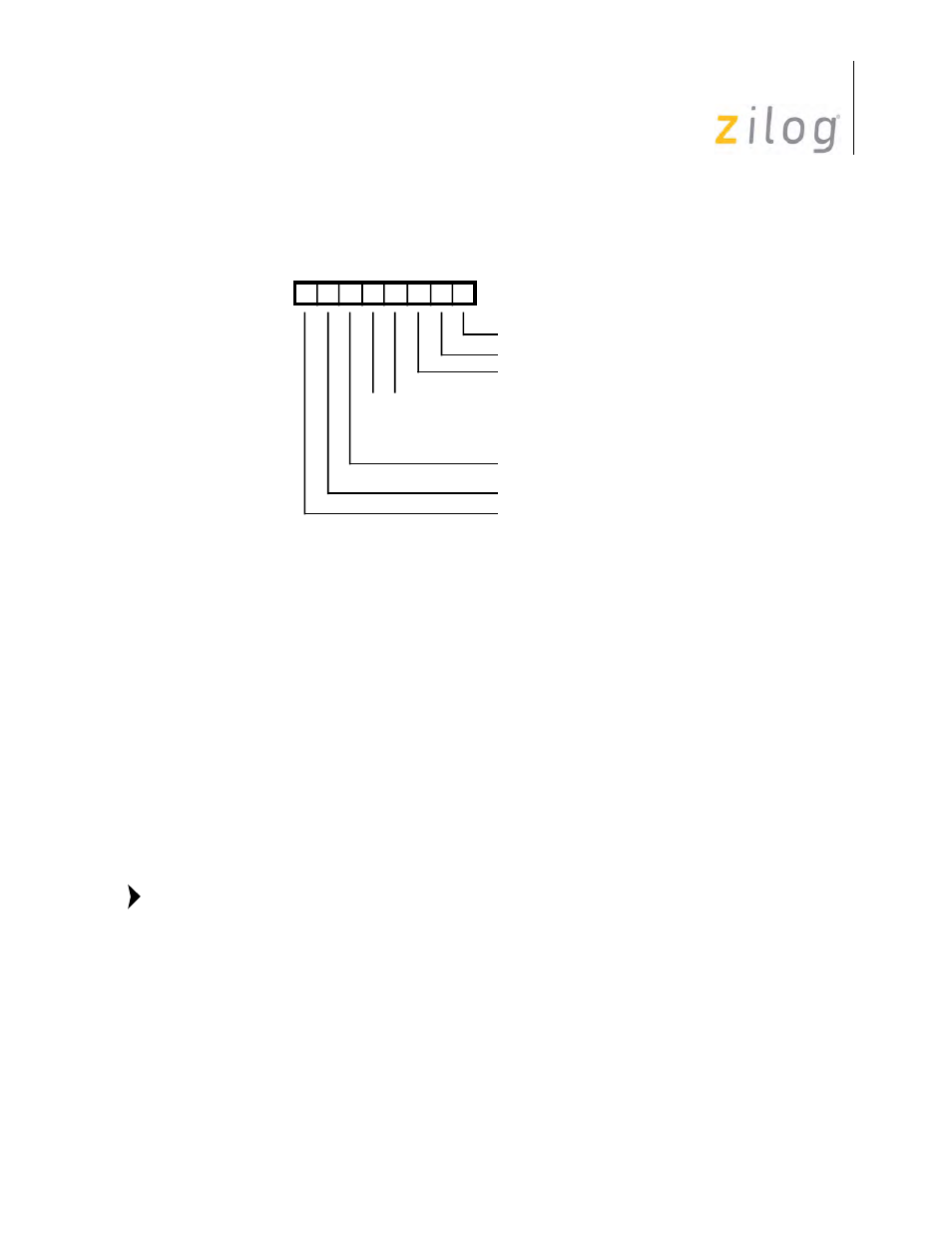

D7 D6 D5 D4 D3 D2 D1 D0

Write Register 1

Ext Int Enable

Tx Int Enable

Parity is Special Condition

0 0 Rx Int Disable

0 1 Rx Int On First Character or Special Condition

1 0 Int On All Rx Characters or Special Condition

1 1 Rx Int On Special Condition Only

WAIT/DMA Request On

Receive//Transmit

/WAIT/DMA Request Function

WAIT/DMA Request Enable

Note: