Table, Is displayed in, Figure – Zilog Z80230 User Manual

Page 170

SCC/ESCC

User Manual

UM010903-0515

Register Descriptions

163

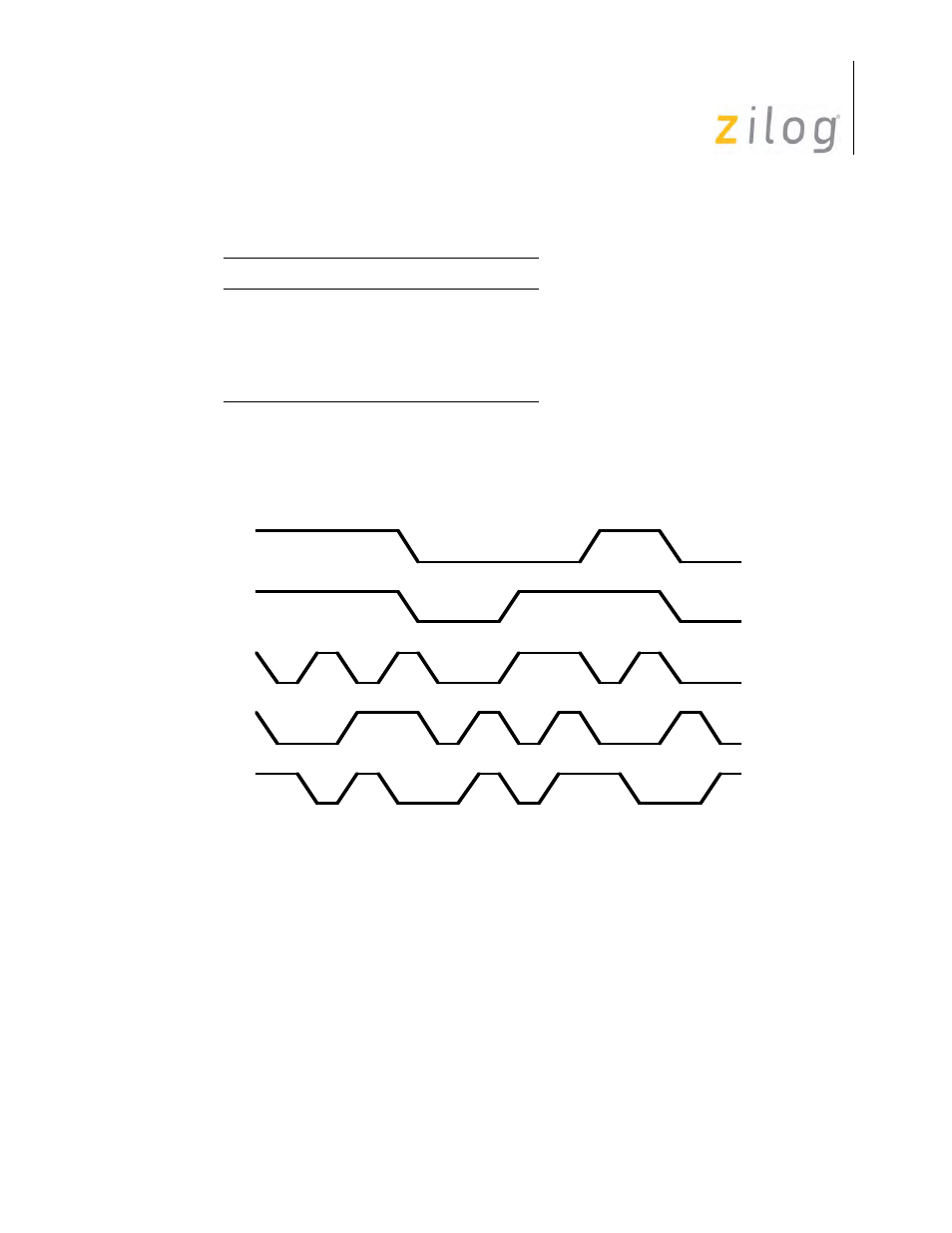

NRZ (NRZI), FM1 (FM0) Timing

Bit 4: Go-Active-On-Poll control bit

When Loop mode is first selected during SDLC operation, the SCC connects RxD to TxD with

only gate delays in the path. The SCC does not go on-loop and insert the 1-bit delay between RxD

and TxD until this bit has been set and an EOP received. When the SCC is on-loop, the transmitter

does not go active unless this bit is set at the time an EOP is received. The SCC examines this bit

whenever the transmitter is active in SDLC Loop mode and is sending a flag. If this bit is set at the

time the flag is leaving the Transmit Shift register, another flag or data byte (if the transmit buffer

is full) is transmitted.

If the Go-Active-On-Poll bit is not set at this time, the transmitter finishes sending the flag and

reverts to the 1-Bit Delay mode. Thus, to transmit only one response frame, this bit is reset after

Data Encoding

Bit 6

Bit 5

Encoding

0

0

NRZ

0 1

NRZI

1

0

FM1 (transition = 1)

1

1

FM0 (transition = 0)

Data

NRZ

NRZI

FM1

FM0

1

1

0

0

1

0

Manchester