Ted (see, Figure – Zilog Z80230 User Manual

Page 75

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

68

from the time the character with the special receive condition is read, and the FIFO locked, until

after the Error Reset command has been issued.

DMA Receive Request Assertion

Once the FIFO is locked, it allows the checking of the Receive Error FIFO (RR1) to find the cause

of the error. Locking the data FIFO, therefore, stops the error status from popping out of the

Receive Error FIFO. Also, since the DMA request becomes inactive, the interrupt (Special Condi-

tion) is serviced.

Once the FIFO is unlocked by the Error Reset command, /REQ again follows the state of the

receive buffer. In the case of the Z80X30, /REQ goes High in response to the falling edge of /DS,

but only if the appropriate receive buffer in the SCC is accessed (

). In the case of the

Z85X30, /REQ goes High in response to the falling edge of /RD, but only when the appropriate

receive buffer in the SCC is accessed (See

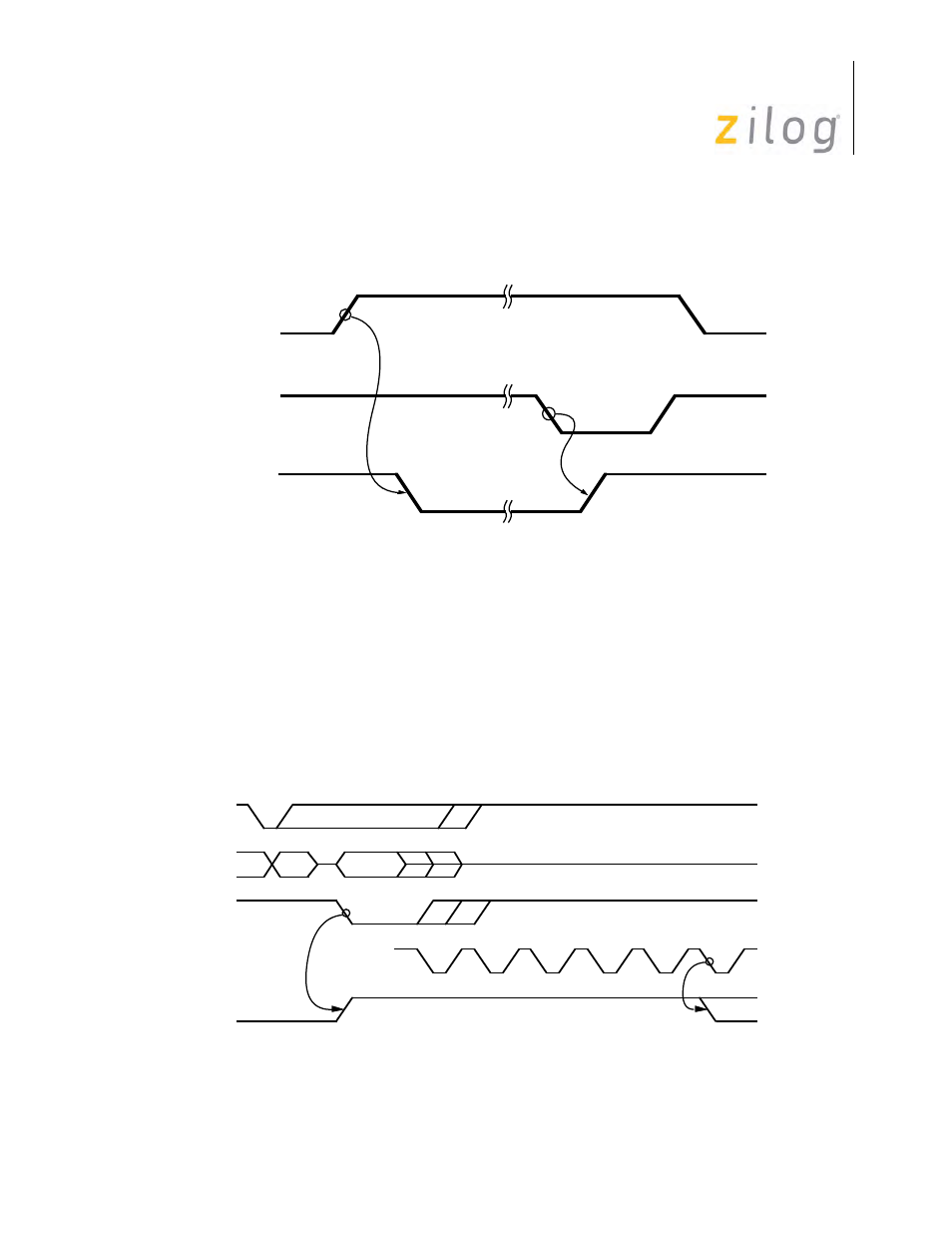

Z80X30 Receive Request Release

Read Strobe

to FIFO

Rx Character

Available

W/REQ

(=REQ)

Character Available

FIFO

Empty

/DS

PCLK

/AS

AD7-AD0

Receive Data

WR8

/REQ