Z80230 register enhancements – Zilog Z80230 User Manual

Page 32

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

25

Z80230 Register Enhancements

In addition to the Z80C30 enhancements, the 80230 has several enhancements to the SCC register

set. These include the addition of Write Register 7 Prime (WR7'), and the ability to read registers

that are read only in the 8030.

Write Register 7' is addressed by setting WR15 bit, D0=1 and then addressing WR7.

plays the register bit location of the six features enabled through this register. All writes to address

seven are to WR7' when WR15, D0=1. Refer to

on page 136 for detailed

information on WR7'.

Write Register 7 Prime (WR7')

WR7' bit D6=1, enables the extended read register capability. This allows the user to read the con-

tents of WR3, WR4, WR5, WR7' and WR10 by reading RR9, RR4, RR5, RR14 and RR11, respec-

tively. When WR7' D6=0, these write registers are write only.

lists what functions are enabled for the various combinations of register bit enables. See

on page 23 (Shift Right) for the register address map with

the SDLC FIFO enabled only and the map with both the extended read and SDLC FIFO features

enabled.

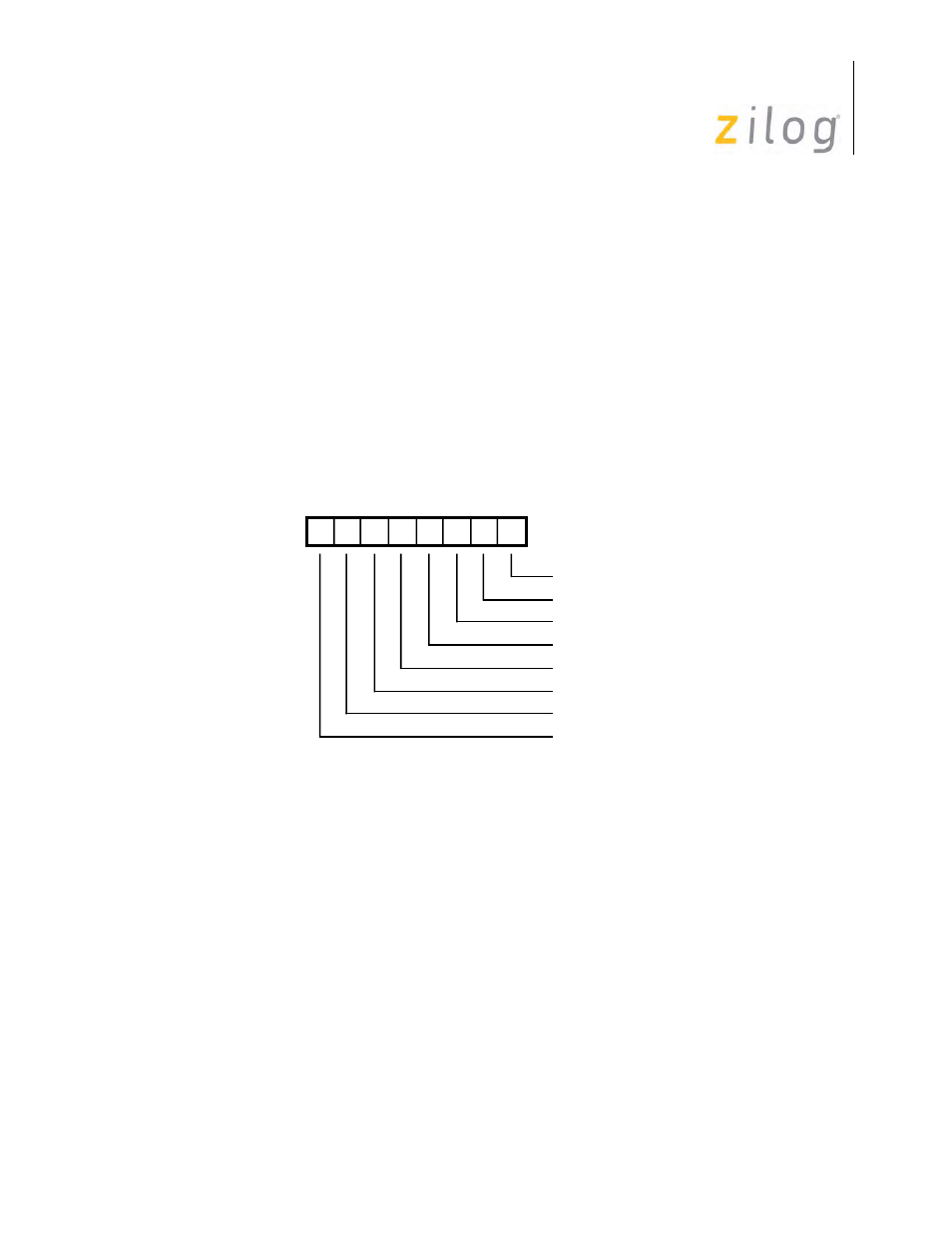

D7 D6 D5 D4 D3 D2 D1 D0

WR7'

Auto Tx Flag

Auto EOM Reset

Auto RTS Turnoff

Rx FIFO Half Full

DTR/REQ Timing M

Tx FIFO Empty

External Read Enab

0