Read register 1 – Zilog Z80230 User Manual

Page 185

SCC/ESCC

User Manual

UM010903-0515

Register Descriptions

178

Read Register 1

RR1 contains the Special Receive Condition status bits and the residue codes for the l-field in

SDLC mode.

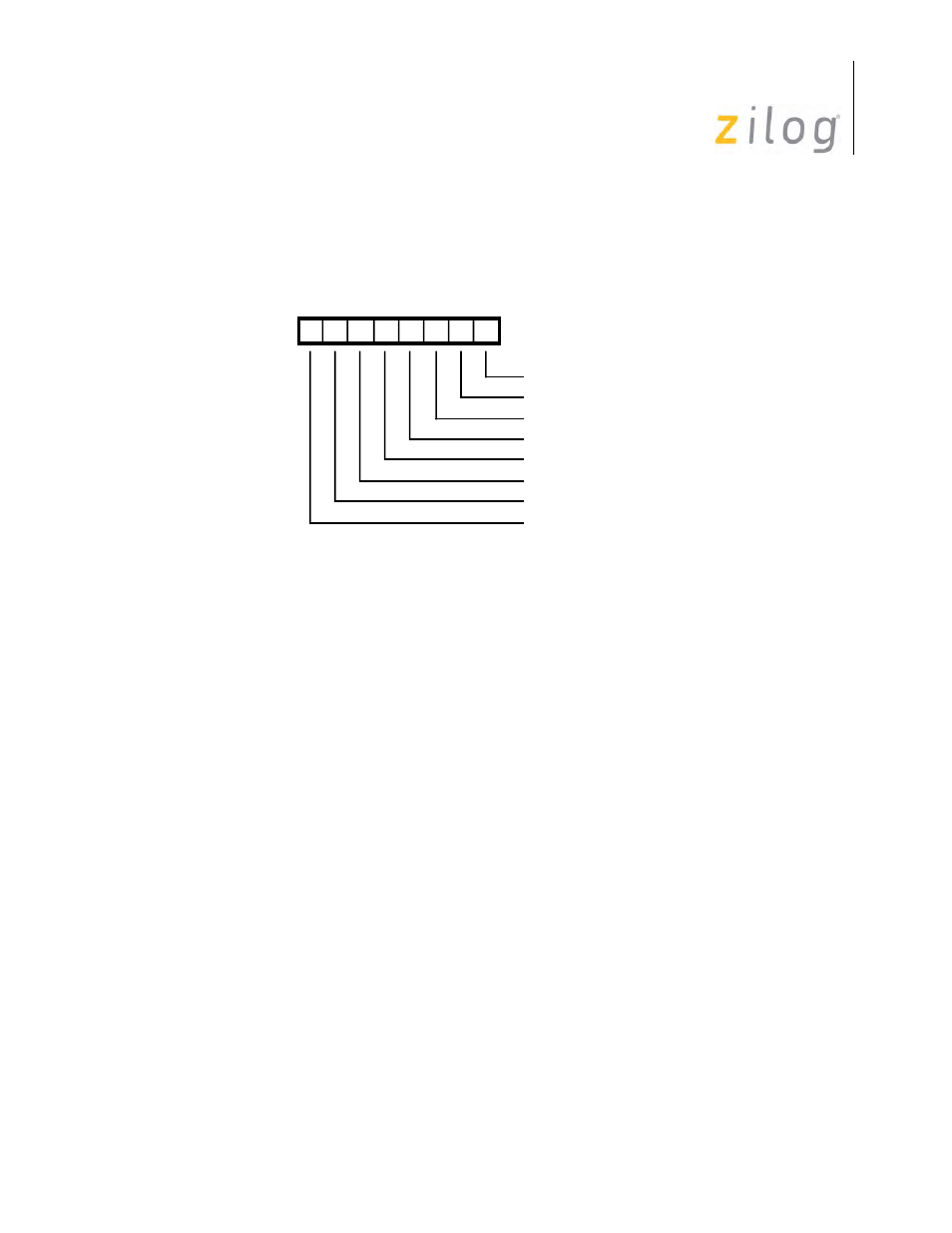

displays the bit positions for RR1.

Read Register 1

Bit 7: End of Frame (SDLC) status

This bit is used only in SDLC mode and indicates that a valid closing flag has been received and

that the CRC Error bit and residue codes are valid. This bit is reset by issuing the Error Reset com-

mand. It is also updated by the first character of the following frame. This bit is reset in any mode

other than SDLC.

Bit 6: CRC/Framing Error status

If a framing error occurs (in Asynchronous mode), this bit is set (and not latched) for the receive

character in which the framing error occurred. Detection of a framing error adds an additional one-

half bit to the character time so that the framing error is not interpreted as a new Start bit. In Syn-

chronous and SDLC modes, this bit indicates the result of comparing the CRC checker to the

appropriate check value. This bit is reset by issuing an Error Reset command, but the bit is never

latched. Therefore, it is always updated when the next character is received. When used for CRC

error status in Synchronous or SDLC modes, this bit is usually set since most bit combinations,

except for a correctly completed message, result in a nonzero CRC.

On the CMOS and ESCC, if the Status FIFO is enabled (refer to the description in Write Register

15, bit D2 and the description in Read Register 7, bits D7 and D6), this bit reflects the status stored

at the exit location of the Status FIFO.

D7 D6 D5 D4 D3 D2 D1 D0

Read Register 1

All Sent

Residue Code 2

Residue Code 1

Residue Code 0

Parity Error

Rx Overrun Error

CRC/Framing Error

End of Frame (SDLC)