Zilog Z80230 User Manual

Page 163

SCC/ESCC

User Manual

UM010903-0515

Register Descriptions

156

tion in the section on Write Register 15. Features enabled in WR7 Prime remain enabled unless

otherwise disabled; a hardware or channel reset leaves WR7 Prime with all features intact (register

contents are 0) (See

Write Register 7 Prime

Bit 7: Reserved

This bit is not used and must always be written zero.

Bit 6: Extended Read Enable bit

Setting this bit enables the reading of WR3, WR4, WR5, WR7 Prime and WR10. When this fea-

ture is enabled, these registers can be accessed by reading RR9, RR4, RR5, RR14, and RR11,

respectively. When the extended read is not enabled, register access is identical to that of the

NMOS/CMOS version. See

on page 17 on how this feature affects the

mapping of read registers.

Bit 5: Transmit FIFO Interrupt Level

If this bit is set, the transmit buffer empty interrupt is generated when the Transmit FIFO is com-

pletely empty. If this bit is reset (0), the transmit buffer empty interrupt is generated when the

entry location of the Transmit FIFO is empty. This latter operation is identical to that of the

NMOS/CMOS version.

In the DMA Request on Transmit Mode, when using either the /W//REQ or /DTR//REQ pins, the

request is asserted when the Transmit FIFO is completely empty if the Transmit FIFO Interrupt

Level bit is set. The request is asserted when the entry location of the Transmit FIFO is empty if

the Transmit FIFO Interrupt Level bit is reset (0).

Bit 4: /DTR//REQ Timing

If this bit is set and the /DTR//REQ pin is used for Request Mode (WR14 bit D2 = 1), the deactiva-

tion of the /DTR//REQ pin is identical to the /W//REQ pin. Refer to the chapter on interfacing for

further details. If this bit is reset (0), the deactivation time for the /DTR//REQ pin is 4TcPc. This

latter operation is identical to that of the SCC.

Bit 3: Receive FIFO Interrupt Level

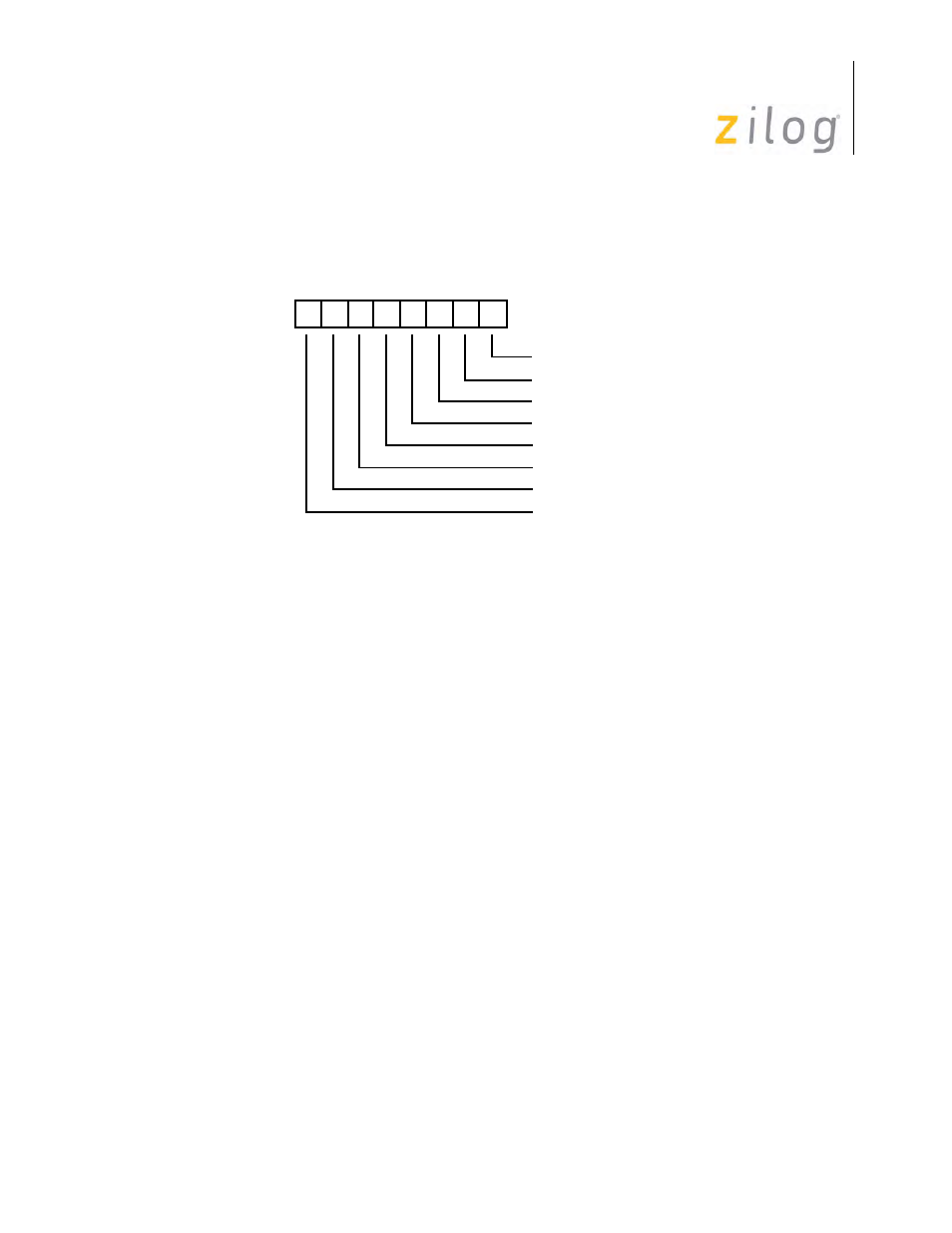

D7 D6 D5 D4 D3 D2 D1 D0

WR7'

Auto Tx Flag

Auto EOM Reset

Auto/RTS Deactivation

Rx FIFO Half Full

DTR/REQ Timing Mode

Tx FIFO Empty

Extended Read Enable

Reserved (Must be 0)