Imately one pclk time), Figure – Zilog Z80230 User Manual

Page 59

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

52

An enhancement to the ESCC from the NMOS/CMOS version is that the CRC has priority over

the data, where on the NMOS/CMOS version data has priority over the CRS. This means that on

the ESCC the CRC bytes are guaranteed to be sent, even if the data for the next packet has written

before the second transmit interrupt, but after the EOM/Underrun condition exists. This helps to

increase the system throughput because there is not waiting for the second transmit interrupt. On

the NMOS/CMOS version, if the data is written while the CRC is sent, CRC byte(s) are replaced

with the flag/sync pattern followed by the data.

Another enhancement of the ESCC is that it latches the transmit interrupt because the CRC is

loaded into the Transmit Shift Register even if the transmit interrupt, due to the last data byte, is

not yet reset. Therefore, the end of a synchronous frame is guaranteed to generate two transmit

interrupts even if a Reset Tx Int Pending command for the data created interrupt is issued after

(Time “A” in

on page 52) the CRC interrupt had occurred. In this case, two reset Tx Int

Pending commands are required. The TxIP is latched if the EOM latch has been reset before the

end of the frame.

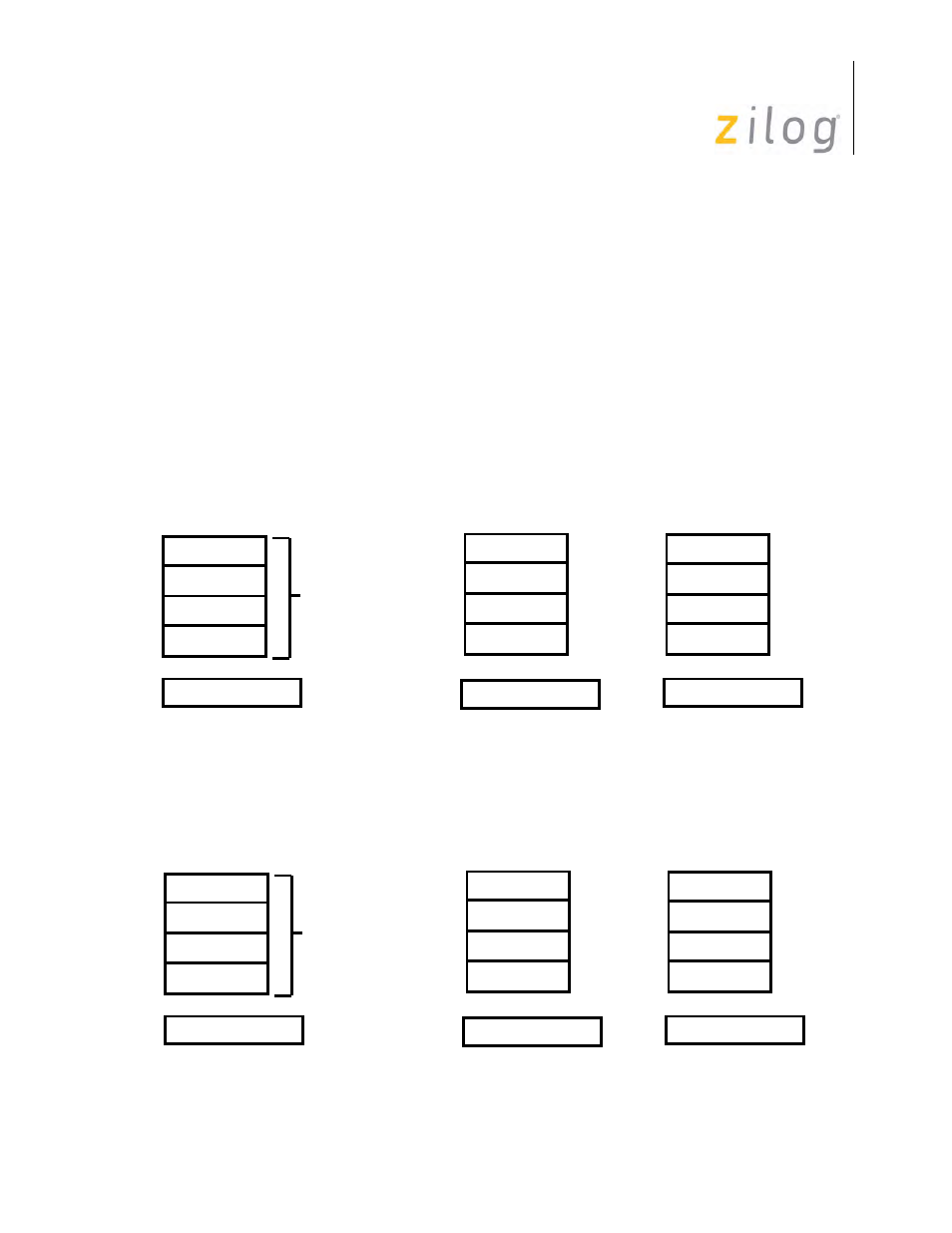

Transmit Interrupt Status When WR7’ D5=1 For ESCC

01

TxFIFO

Tx Shift Register

No Transmit Interrupt

TxIP=0

04

03

02

Transmit Interrupt

TxIP=1

04

03

02

No Transmit Interrupt

TxIP=0

01

TxFIFO

Tx Shift Register

TBE=0

04

03

02

TBE=1

04

03

02

TBE=1

Opening Flag

01

04

03

02