Transmit interrupts and transmit buffer empty bit, Transmit interrupts and transmit buffer empty, Figure – Zilog Z80230 User Manual

Page 56: Scc/escc user manual

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

49

unlock it. Only the exit location of the FIFO is locked allowing more data to be

received into the other bytes of the Receive FIFO.

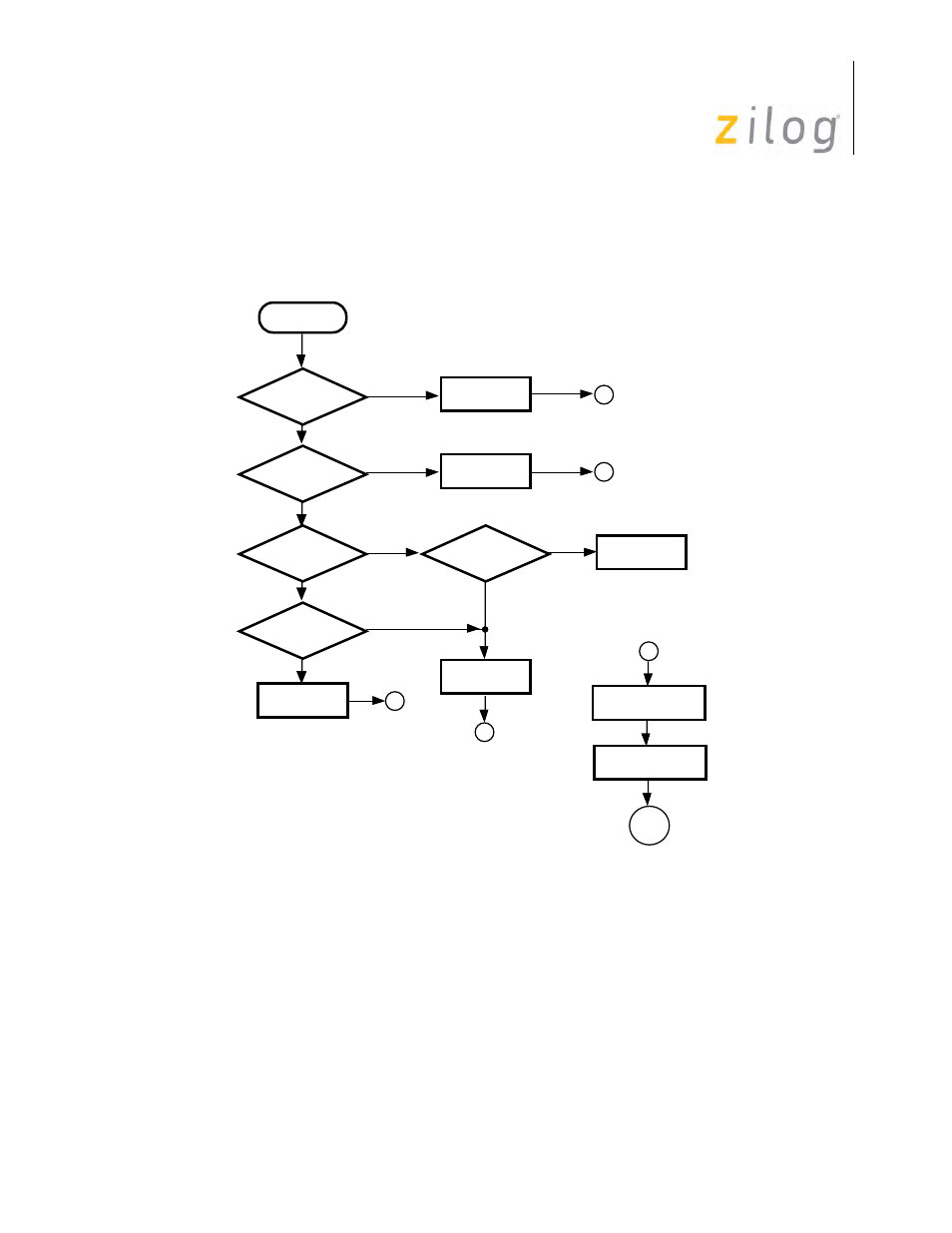

Special Conditions Interrupt Service Flow

Transmit Interrupts and Transmit Buffer Empty Bit

Transmit interrupts are controlled by Transmit Interrupt Enable bit (D1) in WR1. If the interrupt

capabilities of the SCC are not required, polling may be used. This is selected by disabling trans-

mit interrupts and polling the Transmit Buffer Empty bit (TBE) in RR0. When the TBE bit is set, a

character may be written to the SCC without fear of writing over previous data. Another way of

polling the SCC is to enable transmit interrupts and then reset Master Interrupt Enable bit (MIE) in

WR9. The processor may then poll the IP bits in RR3A to determine when the transmit buffer is

Special

Condition

Error Handli

Is It

Parity

(RR1 Bit 4)?

Is It

Overrun

(RR1 Bit 5)?

Reads Dat

Characte

Re

Reset Highest I

(WR0 - 38)

No

Yes

Yes

Is It

EOF

(RR1 Bit 7

Is It

Framing

(RR1 Bit 6)

Error Handli

Yes

Error Handli

Good Messag

Yes

Is It

CRC Error

(RR1 Bit 6)?

1

Error Handli

No

No

1

1

1

1

No

No