Altera IP Compiler for PCI Express User Manual

Page 103

Chapter 5: IP Core Interfaces

5–17

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

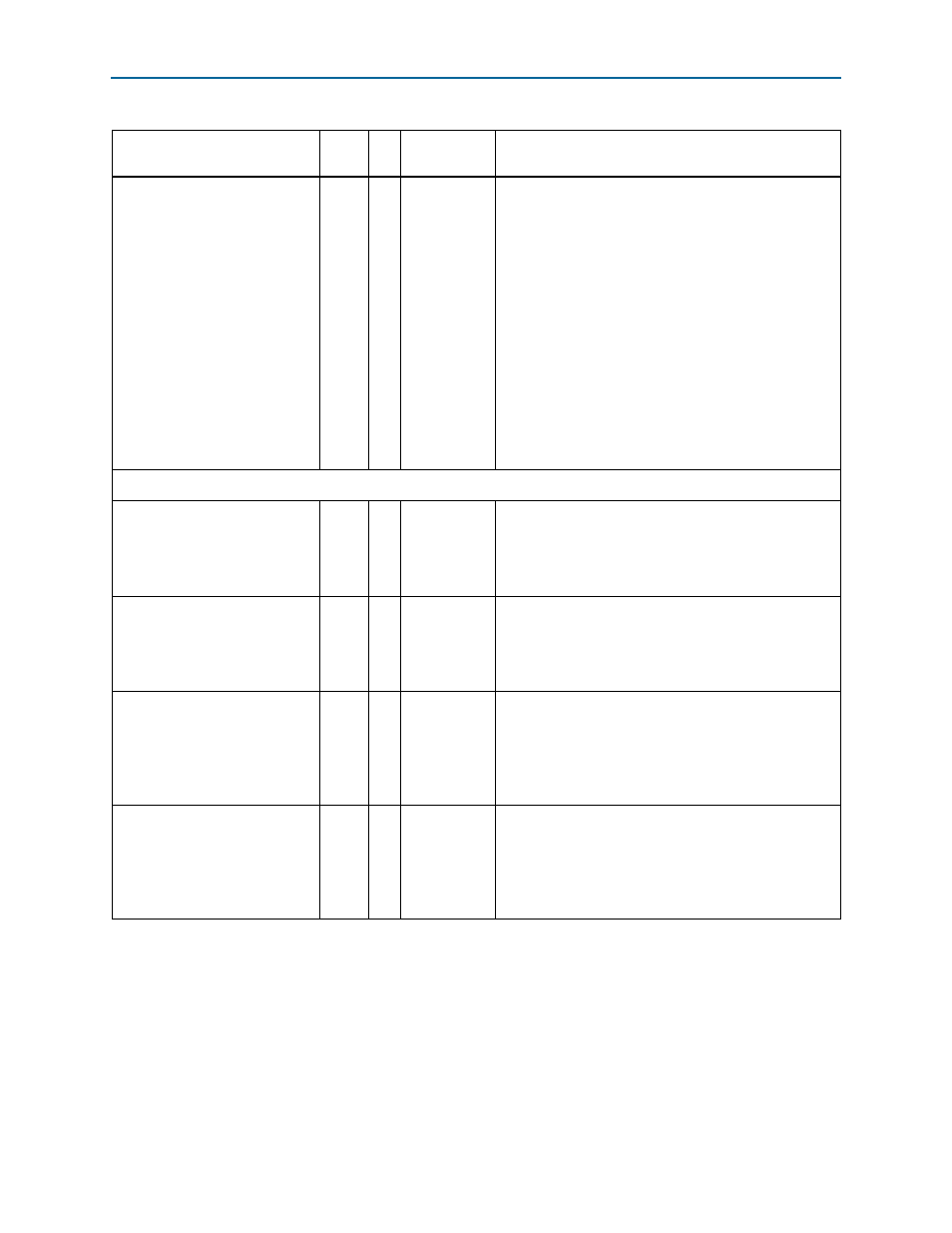

36

O

component

specific

This vector contains the available header and data credits

for each type of TLP (completion, non-posted, and

posted). Each data credit is 4 dwords or 16 bytes as per

the PCI Express Base Specification. Use of the signal is

optional.

If more TX credits are available than the tx_cred bus can

display, tx_cred shows the maximum number given the

number of bits available for that particular TLP type.

tx_cred

is a saturating bus and for a given TLP type, it

does not change until enough credits have been

consumed to fall within the range tx_cred can display.

for the layout of fields in this signal.

For information about how to use the tx_cred signal to

optimize flow control, refer to

Component Specific Signals for Arria II GX, Arria II GZ, and Stratix IV Devices

1

O

component

specific

Used in conjunction with the optional tx_cred<n>

signal. When 1, indicates that the non-posted header

credit limit was initialized to only 1 credit. This signal is

asserted after FC Initialization and remains asserted until

the link is reinitialized.

npd_alloc_1cred_vc0

1

O

component

specific

Used in conjunction with the optional tx_cred<n>

signal. When 1, indicates that the non-posted data credit

limit was initialized to only 1 credit. This signal is

asserted after FC Initialization and remains asserted until

the link is reinitialized.

npd_cred_vio_vc0

1

O

component

specific

Used in conjunction with the optional tx_cred<n>

signal. When 1, means that the non-posted data credit

field is no longer valid so that more credits were

consumed than the tx_cred signal advertised. Once a

violation is detected, this signal remains high until the IP

core is reset.

nph_cred_vio_vc0

1

O

component

specific

Used in conjunction with the optional tx_cred<n>

signal. When 1, means that the non-posted header credit

field is no longer valid. This indicates that more credits

were consumed than the tx_cred signal advertised.

Once a violation is detected, this signal remains high until

the IP core is reset.

Notes to

(1) For all signals, <n> is the virtual channel number, which can be 0 or 1.

(2) To be Avalon-ST compliant, you must use a readyLatency of 1 or 2 for hard IP implementation, and a readyLatency of 1 or 2 or 3 for the

soft IP implementation. To facilitate timing closure, Altera recommends that you register both the tx_st_ready and tx_st_valid signals. If

no other delays are added to the ready-valid latency, this corresponds to a readyLatency of 2.

(3) For the completion header, posted header, non-posted header, and non-posted data fields, a value of 7 indicates 7 or more available

credits.

(4) These signals only apply to hard IP implementations in Arria II GX and Stratix IV GX devices.

(5) In Stratix IV and Arria II GX hard IP implementations, the non-posted TLP credit field is valid for systems that support more than 1 NP credit.

In systems that allocate only 1 NP credit, the receipt of completions should be used to detect the credit release.

(6) These signals apply only to hard IP implementations in Arria II GX and Stratix IV devices.

Table 5–4. 64- or 128-Bit Avalon-ST TX Datapath (Part 3 of 3)

Signal

Width

Dir

Avalon-ST

Type

Description