Clocks, Avalon-st interface—hard ip implementation, Is also provided in – Altera IP Compiler for PCI Express User Manual

Page 169

Chapter 7: Reset and Clocks

7–5

Clocks

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Clocks

This section describes clocking for the IP Compiler for PCI Express. It includes the

following sections:

■

Avalon-ST Interface—Hard IP Implementation

■

Avalon-ST Interface—Soft IP Implementation

■

Clocking for a Generic PIPE PHY and the Simulation Testbench

■

Avalon-MM Interface–Hard IP and Soft IP Implementations

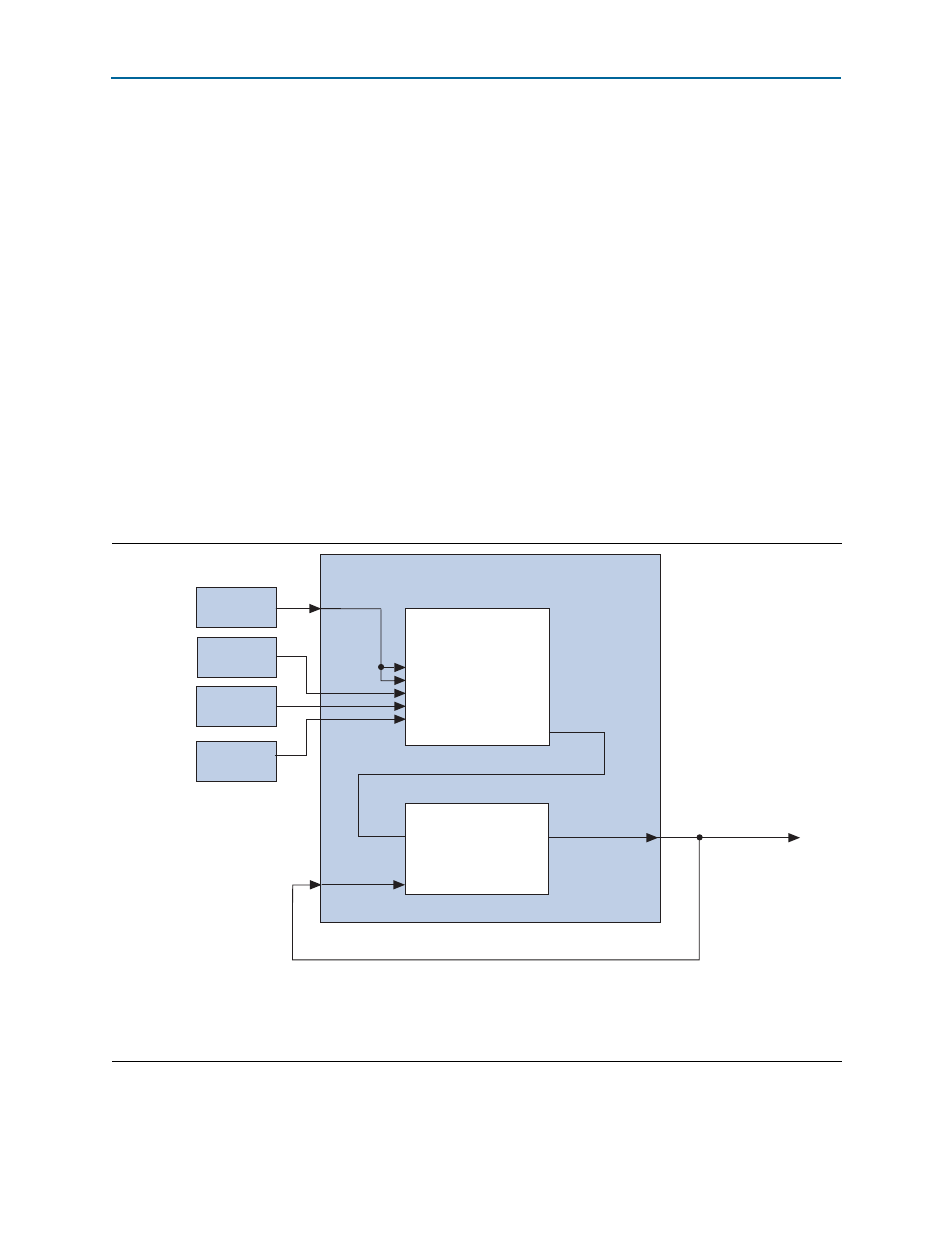

Avalon-ST Interface—Hard IP Implementation

When implementing the Arria II GX, Cyclone IV GX, HardCopy IV GX, or

Stratix IV GX PHY in a ×1 or ×4 configuration, the 100 MHz reference clock is

connected directly to the transceiver. core_clk_out is driven by the output of the

transceiver. core_clk_out must be connected back to the pld_clk input clock,

possibly through a clock distribution circuit required by the specific application. The

user application interface is synchronous to the pld_clk input.

illustrates this clocking configuration.

Figure 7–4. Arria II GX, Arria II GZ, Cyclone IV GX, HardCopy IV GX, Stratix IV GX ×1, ×4, or ×8 100 MHz Reference Clock

Notes to

(1) Different device families require different frequency ranges for the calibration and reconfiguration clocks. To determine the frequency range for

your device, refer to one of the following device handbooks:

olume II of the Arria II Device Handbook,

in Volume 2 of the Cyclone IV Device Handbook, or

Volume 2 of the Stratix IV Device Handbook.

(2) Refer to

for information about the core_clk_out frequencies for different device families and variations.

100-MHz

Clock Source

Calibration

Clock Source

Reconfig

Clock Source

Fixed

Clock Source

refclk

Application Clock

pld_clk

Note (1)

tx_clk_out

<variant>_serdes.v or .vhd

(ALTGX or ALT2GX

Megafunction)

<variant>.v or .vhd

<variant>_core.v or .vhd

(PCIe MegaCore Function)

rx_cruclk

pll_inclk

cal_blk_clk

reconfig_clk

fixedclk

core_clk_out (2)

125 MHz - x1,x4,x8

62.5 MHz - x1

250 MHz - x8