Error handling – Altera IP Compiler for PCI Express User Manual

Page 203

August 2014

Altera Corporation

IP Compiler for PCI Express U

12. Error Handling

Each PCI Express compliant device must implement a basic level of error

management and can optionally implement advanced error management. The Altera

IP Compiler for PCI Express implements both basic and advanced error reporting.

Given its position and role within the fabric, error handling for a root port is more

complex than that of an endpoint.

The PCI Express specifications defines three types of errors, outlined in

.

The following sections describe the errors detected by the three layers of the PCI

Express protocol and describes error logging. It includes the following sections:

■

■

■

■

Error Reporting and Data Poisoning

■

Uncorrectable and Correctable Error Status Bits

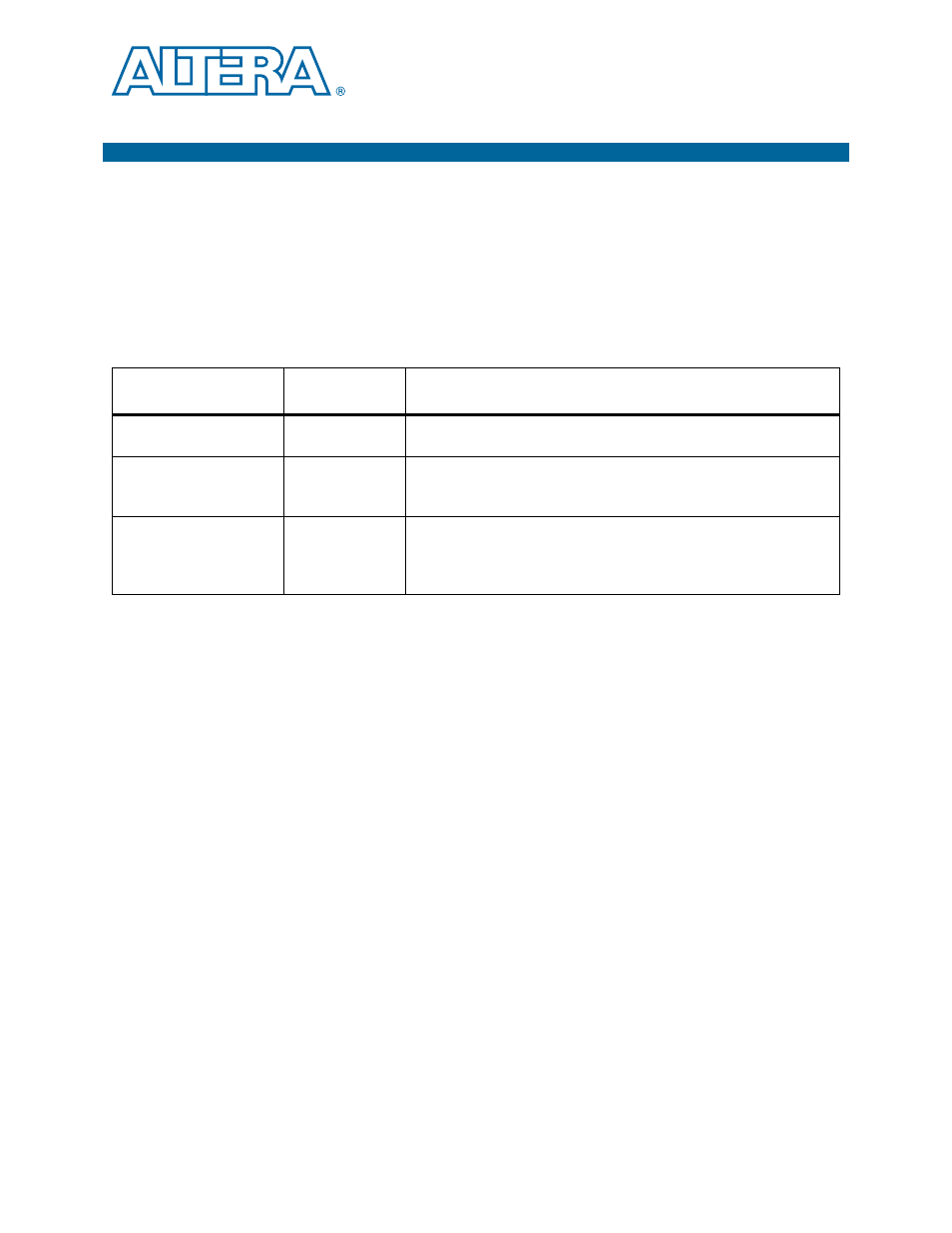

Table 12–1. Error Classification

Type

Responsible

Agent

Description

Correctable

Hardware

While correctable errors may affect system performance, data integrity is

maintained.

Uncorrectable, non-fatal

Device software

Uncorrectable, non-fatal errors are defined as errors in which data is lost,

but system integrity is maintained. For example, the fabric may lose a

particular TLP, but it still works without problems.

Uncorrectable, fatal

System software

Errors generated by a loss of data and system failure are considered

uncorrectable and fatal. Software must determine how to handle such

errors: whether to reset the link or implement other means to minimize

the problem.

August 2014

<edit Part Number variable in chapter>