Altera IP Compiler for PCI Express User Manual

Page 331

Chapter :

B–13

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

describes the standard TX data phase signals.

tx_desc<n>[127:0]

(cont.)

I

Bit 126 of the descriptor indicates the type of transaction layer packet in transit:

■

tx_desc[126]

when 0: transaction layer packet without data

■

tx_desc[126]

when 1: transaction layer packet with data

The following list provides a few examples of bit fields on this bus:

■

tx_desc[105:96]: length[9:0]

■

tx_desc[126:125]: fmt[1:0]

■

tx_desc[126:120]: type[4:0]

tx_ack<n>

O

Transmit acknowledge. This signal is asserted for one clock cycle when the IP core

acknowledges the descriptor phase requested by the application through the tx_req

signal. On the following clock cycle, a new descriptor can be requested for transmission

through the tx_req signal (kept asserted) and the tx_desc.

Note to

(1) For all signals, <n> is the virtual channel number which can be 0 or 1.

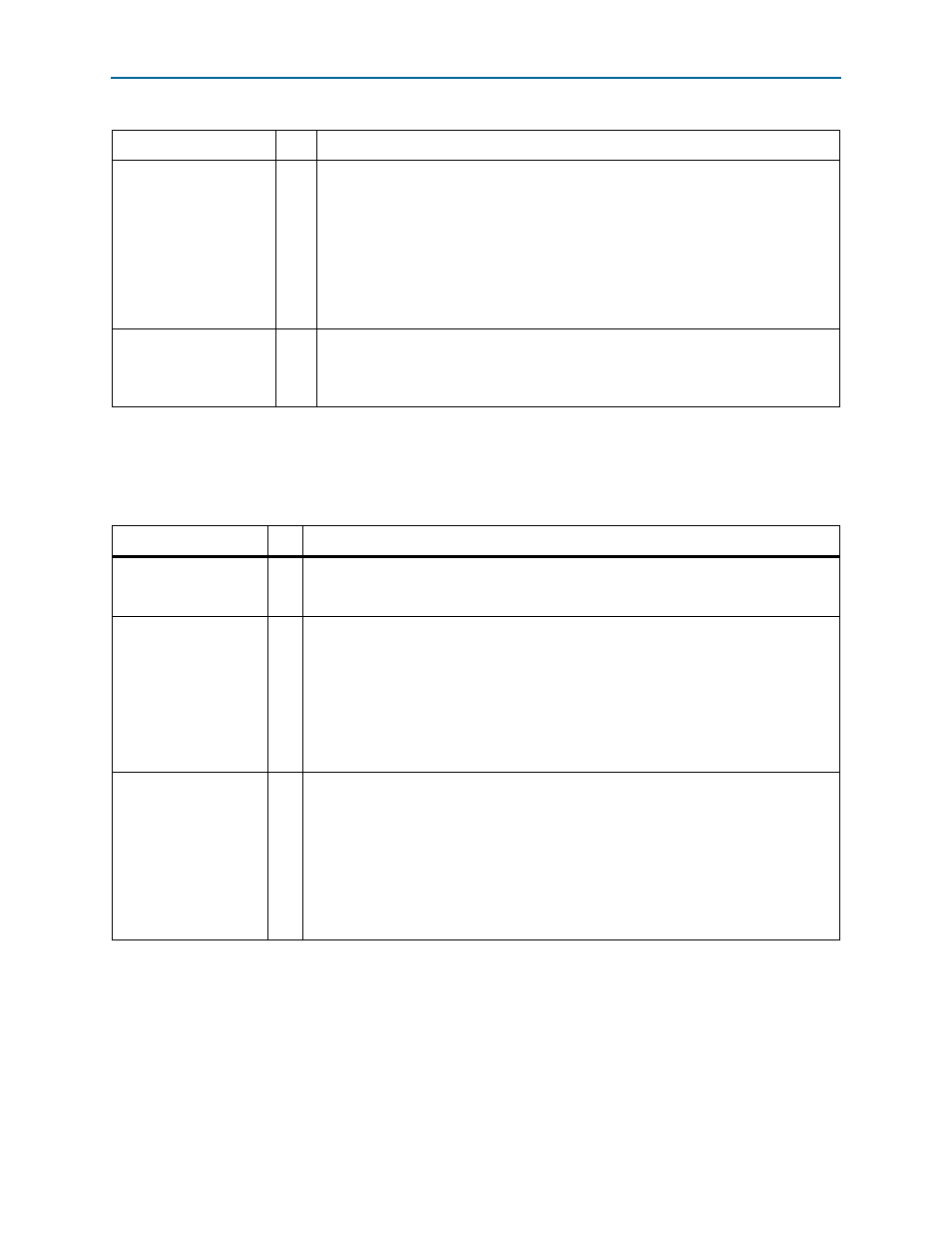

Table B–6. Standard TX Descriptor Phase Signals (Part 2 of 2)

Signal I/O

Description

Table B–7. Standard TX Data Phase Signals (Part 1 of 2)

Signal

I/O

Description

tx_dfr<n>

I

Transmit data phase framing. This signal is asserted on the same clock cycle as tx_req to

request a data phase (assuming a data phase is needed). This signal must be kept asserted

until the clock cycle preceding the last data phase.

tx_dv<n>

I

Transmit data valid. This signal is asserted by the user application interface to signify that

the tx_data[63:0] signal is valid. This signal must be asserted on the clock cycle

following assertion of tx_dfr until the last data phase of transmission. The IP core

accepts data only when this signal is asserted and as long as tx_ws is not asserted.

The application interface can rely on the fact that the first data phase never occurs before a

descriptor phase is acknowledged (through assertion of tx_ack). However, the first data

phase can coincide with assertion of tx_ack if the transaction layer packet header is only 3

DWORDS.

tx_ws<n>

O

Transmit wait states. The IP core uses this signal to insert wait states that prevent data

loss. This signal might be used in the following circumstances:

■

To give a DLLP transmission priority.

■

To give a high-priority virtual channel or the retry buffer transmission priority when the

link is initialized with fewer lanes than are permitted by the link.

If the IP core is not ready to acknowledge a descriptor phase (through assertion of tx_ack

on the following cycle), it will automatically assert tx_ws to throttle transmission. When

tx_dv

is not asserted, tx_ws should be ignored.